## 10GBASE-LRM-LR X2 Transponder

## (BBTR10310MS-X1)

#### PRELIMINARY SPECIFICATIONS - SUBJECT TO CHANGE

Rev 0.5a, (updated 8/15/2005) Contact <a href="mailto:support@bigbearnetworks.com">support@bigbearnetworks.com</a> for further information

This document provides the specifications for the Big Bear Networks 10GBASE-LRM-LR X2 transponder which meets the IEEE802.3aq D2.2 draft standard for LRM links as well as the IEEE standard for LR links.

## **Features**

- Electro-optical X2 transponder operating at 10.3125 Gb/s

- Supports 10GE LAN PHY (10GBASE-R per Clause 49 of IEEE P802.3ae-2002)

- Hot Pluggable

- Incorporates Big Bear Electronic Dispersion Compensation for robust operation over 300m of installed multimode fiber

- Five diagnostic loop-back modes

- Class I laser

- Compatible with Applicable Industry Standards:

- XAUI Interface per Clause 47 of IEEE P802.3ae-2002

- MDIO Interface per Clause 45 of IEEE P802.3ae-2002

- X2 MSA, Issue 1.0, 2003

- IEEE802.3aq (Draft 2.2) for LRM links

- IEEE802.3ae-2002 for LR links

## Applications

- Enterprise networks (wiring closet to core)

- LAN networks and Metro Edge

Figure 1: The Big Bear Networks X2 Transponder

NOTE: THE X2 TRANSPONDER IS ALSO AVAILABLE IN THE MID AND TALL HEAT SINK FORMATS

10BASE-LRM-LR X2 Rev 0.5a, 8/15/05

## Contents

| Features                                            | 1  |  |

|-----------------------------------------------------|----|--|

| Applications                                        | 1  |  |

| General Description                                 | 3  |  |

| Block Diagram Description                           | 4  |  |

| Pin Descriptions                                    |    |  |

| MDIO Interface                                      |    |  |

| Module Management                                   |    |  |

| Power and Ground                                    |    |  |

| Signal Detect Status Registers                      |    |  |

| Link Alarm Status Interrupt                         |    |  |

| Loop-back Modes                                     |    |  |

| Absolute Maximum Ratings                            |    |  |

| Recommended Operating Conditions                    |    |  |

| Optical Characteristics                             |    |  |

| Electrical Characteristics                          |    |  |

| Electrical Connector                                |    |  |

| Electrical Pin-Out List                             |    |  |

| Package Outline Diagram                             |    |  |

| Safety                                              |    |  |

| Reliability and Qualification                       |    |  |

| References                                          |    |  |

| Appendix A: MDIO Registers                          |    |  |

| Device 1 PMA/PMD Registers                          | 22 |  |

| Device 3 PCS Registers<br>Device 4 PHY XS Registers | 36 |  |

| Device 4 PHY XS Registers                           | 40 |  |

| DIY DUUI NUUNJ                                      |    |  |

|                                                     |    |  |

## Tables

| Table 1: Data Input and XAUI Interface         Table 2 MDIO Interface Bus            | 5  |

|--------------------------------------------------------------------------------------|----|

| Table 2 MDIO Interface Bus                                                           | 6  |

| Table 3: Power & Ground Signals                                                      | 6  |

| Table 3: Power & Ground Signals         Table 4: Signal Detect Alarm Fault Registers | 7  |

| Table 5: Loop-back Mode Details                                                      | 10 |

| Table 6 Absolute Maximum Ratings                                                     | 11 |

| Table 7 Standard Operating Conditions                                                | 11 |

| Table 8 Turn-On Characteristics                                                      | 11 |

| Table 9: LRM-LR Transponder Optical Characteristics (Common to LRM and LR)           | 12 |

| Table 10: LRM Specific Optical Characteristics                                       |    |

| Table 11: LR Specific Optical Characteristics                                        | 14 |

| Table 12: XAUI Input Interface                                                       | 15 |

| Table 13: XAUI Driver Interface                                                      | 15 |

| Table 14 LV-CMOS Input and Output Characteristics                                    | 15 |

| Table 15 MDIO Input and Output Characteristics                                       | 16 |

| Table 16: Pin-Out List                                                               |    |

| Table 17 Mechanical Dimensions                                                       | 20 |

| Table 18: NVRAM Registers                                                            |    |

| Table 19: Alarm Thresholds (Subject to Change)                                       | 35 |

|                                                                                      |    |

## Figures

| Figure 1: The Big Bear Networks X2 Transponder                            | 1    |

|---------------------------------------------------------------------------|------|

| Figure 2: Block Diagram Showing Electrical and Optical Inputs and Outputs | 3    |

| Figure 3 Adaptable Power Supply (APS) Lines                               | 6    |

| Figure 4: Link Alarm Status Interrupt signal (LASI) Block Diagram         | 8    |

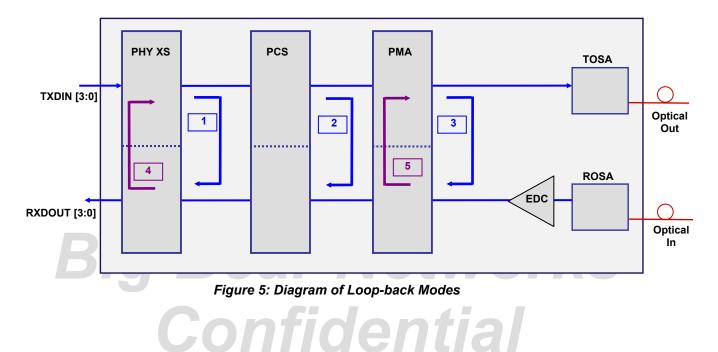

| Figure 5: Diagram of Loop-back Modes                                      | 9    |

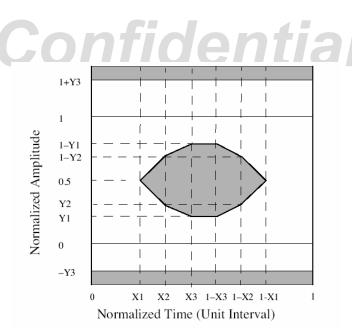

| Figure 6: Transmitter Eye Mask Definition (Per IEEE802.3ae sect 52.9.7)   | . 14 |

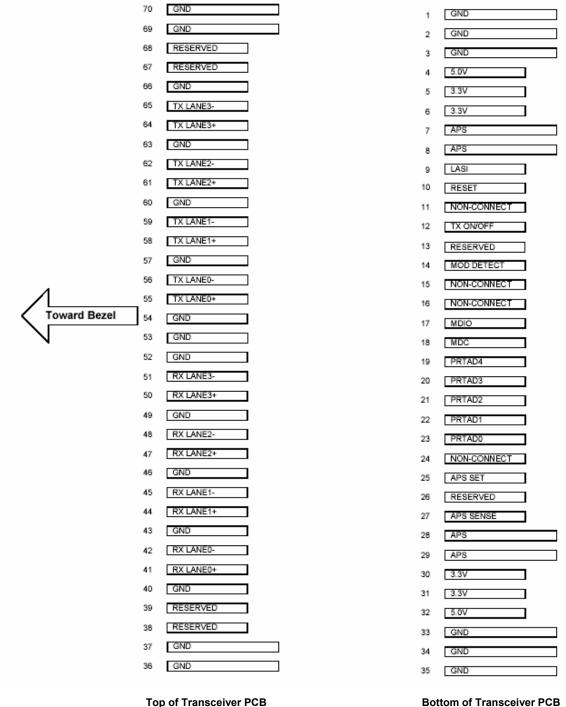

| Figure 7: Electrical Connection Pad Layout                                | . 17 |

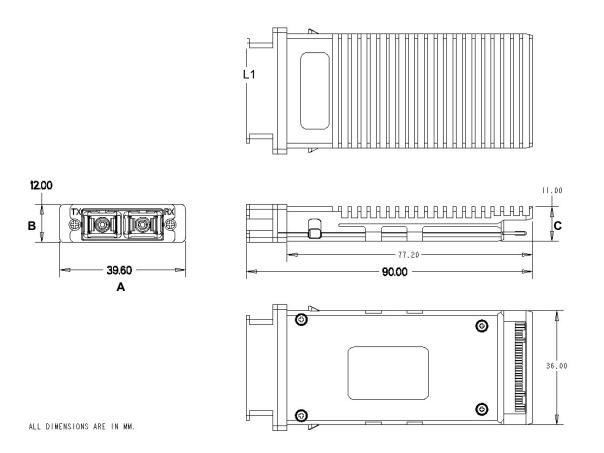

| Figure 8 Transponder Mechanical Drawing                                   | . 20 |

|                                                                           |      |

## **General Description**

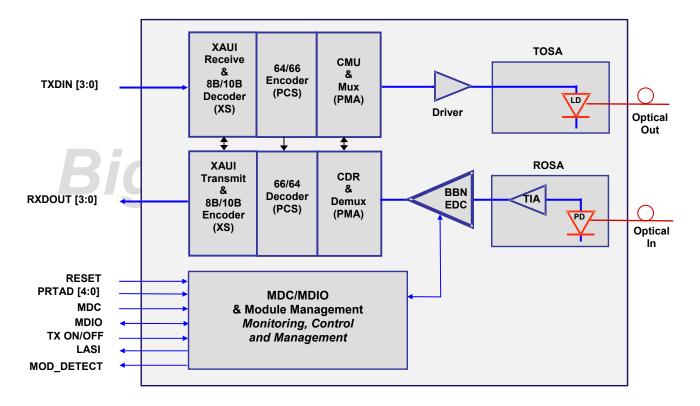

Figure 2 depicts a simplified block diagram of the Big Bear X2 LRM-LR transponder. This bi-directional device provides an electro-optical interface between a serial 10Gb Ethernet optical signal and the XAUI compliant electrical physical layer. The transponder operates the standard 10GbE rate of 10.3125 Gb/s.

A key feature of the BBTR10310MS-X1 is its support for both 300m multimode fiber links as well as single mode fiber links of up to 10km or more.

The Big Bear LRM-LR transponder incorporates the latest generation Big Bear Electronic Dispersion Compensation (EDC) which provides compensation for the severe modal dispersion that may occur during propagation through links up to 300m on legacy installed FDDI multimode fiber (see IEEE802.3aq draft for detailed fiber coverage).

Figure 2: Block Diagram Showing Electrical and Optical Inputs and Outputs

## **Block Diagram Description**

## **XAUI Interface (Input)**

In the optical transmit direction, each 3.125 Gb/s electrical data channel is separately retimed in a clock-and-data recovery block . The retimed data then undergoes Code Alignment and a Lane Deskew before being run through an 8B/10B decoder. The data is rate adjusted then sent through a 64/66B encoder/scrambler, scrambled and finally multiplexed to generate the serial line rate 10.3125 Gb/s electrical signal.

## Transmitter

The multiplexed line rate signal at 10.3125 Gb/s is sent through the modulator driver and the resulting amplified signal used to directly drive the 1.3um DFB laser transmitter in the TOSA package.

## Receiver

In the receive direction, the transponder accepts a 10.3125Gb/s optical signal and converts this to an electrical signal. The optical receiver of the Big Bear LRM-LR transponder incorporates a large area PIN photodiode and a wide-band trans-impedance amplifier (TIA). This receiver is designed to operate with both multimode fiber and single mode fiber. The raw signal output from the TIA is differentially connected to the electronic dispersion compensation (EDC) device.

## **Electronic Dispersion Compensation**

A key feature of the LRM-LR transponder is the incorporation of the advanced Big Bear electronic dispersion compensation (EDC). The Big Bear EDC

device incorporates a Feed Forward Equalizer (FFE) and a Decision Feedback Equalizer (DFE). This architecture provides the high level of compensation required to compensate for the modal dispersion and ISI encountered in legacy FDDI 220m OM1 and OM2 multimode fiber links (300m on OM3). The Big Bear EDC also contains a sophisticated clock recovery architecture for extracting a robust clock from extremely distorted signals.

The Big Bear EDC uses sophisticated adaptive control with rapid tracking time to ensure that the optical link is always tuned for optimal performance.

The DFE block includes the limiting amplifier – ensuring that the slicing decisions are made when the analog eye quality is at its highest level in the receive chain.

## XAUI Interface (Output)

Following the EDC the line rate data is sent through the descrambler, 64/66B decoder, 8B/10B encoder, and XAUI serializer. Each XAUI output lane incorporates a transmit equalizer and electrical output driver for optimal signal performance.

## **MDIO Management Interface**

The MDIO interface provides a simple, two wire serial interface to connect a station management entity (STA) and a managed PHY. The management interface consists of the two wire physical interface, a frame format, a protocol specification for exchanging the frames, and a register set that can be read and written using these frames. The two wires of the physical interface are the Management Data Clock (MDC) and the Management Data I/O (MDIO).

A complete list of the supported MDIO registers is given in Appendix A.

## **Pin Descriptions**

| Name            | I/O | Pins                                 | Туре         | Description                                                                                                                                                                                                                                                                                          |

|-----------------|-----|--------------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXDATA[3:0]_P/N | I   | 55, 56<br>58, 59<br>61, 62<br>64, 65 | Note 1       | <b>Transmit Data.</b> The Transmit Data (TXDATA[3:0]) signals carry data from the system-side ASIC to the XAUI transceiver                                                                                                                                                                           |

| RXDATA[3:0]_P/N | 0   | 41, 42<br>44, 45<br>47, 48<br>50, 51 | Note 2       | <b>Receive Data.</b> The Receive Data (RXDATA[3:0]) signals carry data from XAUI transceiver to the system side ASIC. Per Clause 47 of IEEE P802.3ae-2002 the signal paths are intended to operate up to approximately 50cm over controlled impedance traces on standard FR4 printed circuit boards. |

| LASI            | ο   | 9                                    | 1.2V<br>CMOS | Link Alarm Status Interrupt (LASI)<br>Logic High = normal operation<br>Logic Low = LASI asserted                                                                                                                                                                                                     |

| RESET           | 1   | <sup>10</sup>                        | 1.2V<br>CMOS | Module Reset<br>Logic High = normal operation<br>Logic Low = Reset<br>Minimum transponder reset assert time is 1ms.<br>(10-22K ohm pull-up in transponder)                                                                                                                                           |

| TX ON/OFF       | 1   |                                      | 1.2V<br>CMOS | Transmitter On/Off<br>Logic High = Transmitter on<br>Logic Low = Transmitter off<br>(Open Drain compatible)<br>(10-22K ohm pull-up in transponder)                                                                                                                                                   |

| MOD DETECT      | 0   | 14                                   | NA           | <b>Module Detect.</b> Indicates presence of the module. Pulled low inside the module through 1K                                                                                                                                                                                                      |

Note 1: The XAUI Driver lane electrical characteristics follow the specifications given in Clause 47.3.3 of IEEE P802.3ae-2002.

Note 2: The XAUI Receiver lane electrical characteristics follow the specifications given in Clause 47.3.4 of IEEE P802.3ae-2002.

Note 3: A complete pin list is provided in Table 16: Pin-Out List

## **MDIO Interface**

## Table 2 MDIO Interface Bus

| Name       | I/O | Туре               | Description                               |

|------------|-----|--------------------|-------------------------------------------|

| MDIO       | I/O | MDIO (Note 1)      | Management Data IO                        |

| MDC        | I   | 1.2V CMOS (Note 1) | Management Data Clock                     |

| PRTAD[4:0] | Ι   | 1.2V CMOS (Note 1) | 5 bit address. Low = 0. [1KOhm pull-down] |

Note 1: The transponder adheres to the specification for the MDIO interface in Clause 45 of IEEE P802.3ae-2002.

## **Module Management**

A complete list of the MDIO Registers is provided in Appendix A.

## **Power and Ground**

## Table 3: Power & Ground Signals

| Name      | I/O   | Туре             | Description                                                                                                                                                           |

|-----------|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3V      | - I   | Supply           | Power supply, +3.3V                                                                                                                                                   |

| 5V        | 7 I L | Supply           | Power supply, +5.0V                                                                                                                                                   |

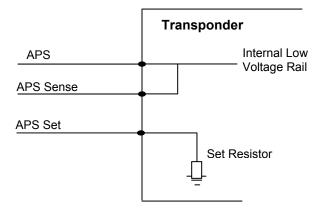

| APS       |       | Supply           | Adaptive Power Supply (1.8V in the Big Bear xR MMF Transponder)                                                                                                       |

| APS Sense | 0     | Analog<br>Signal | Tied to APS power supply rail inside transponder                                                                                                                      |

| APS Set   | 0     | Analog<br>Signal | For this transponder the APS supply needs to be 1.5V, therefore the Set<br>Resistor in the transponder is 1Kohm.<br>The APS circuit in the transponder is shown below |

Figure 3 Adaptable Power Supply (APS) Lines

## Signal Detect Status Registers

When the received optical power drops below a level of  $-15 \pm 1.1$  dBm several alarm registers indicate that there is a loss of signal. The affected registers are listed in Table 4 below. The alarm condition is removed when the received optical power rises above  $-15 \pm 1.1$  dBm. As noted in the table a number of the alarm registers are latching and will only be cleared on a read of that register.

#### Table 4: Signal Detect Alarm Fault Registers

| Parameter                           | Register                  | Register state on Loss<br>of Optical Signal | Indicating                                                                                                                |

|-------------------------------------|---------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Global PMD Receive Signal<br>Detect | 1.10.0<br>(1.0x000A.0)    | 0                                           | Indicates that signal not detected on receiver.<br>This alarm is non-latching.                                            |

| PMA/PMD Fault                       | 1.1.7<br>(1.0x0001.7)     | 1                                           | Indicates a local fault condition in the PMA/PMD<br>This alarm is non-latching.                                           |

| PMA/PMD Receive Fault               | 1.8.10<br>(1.0x0008.10)   | 1                                           | Indicates a fault condition on the receive path<br>(This alarm is latches high and is cleared on a read of this register) |

| Receive Optical Power Fault         | 1.36867.5<br>(1.0x9003.5) |                                             | (This alarm is latches high and is cleared on a read of this register)                                                    |

Note that both the 'Global PMD Receive Signal Detect' and the 'Receive Optical Power Fault' feed into the Link Alarm Status Interrupt.

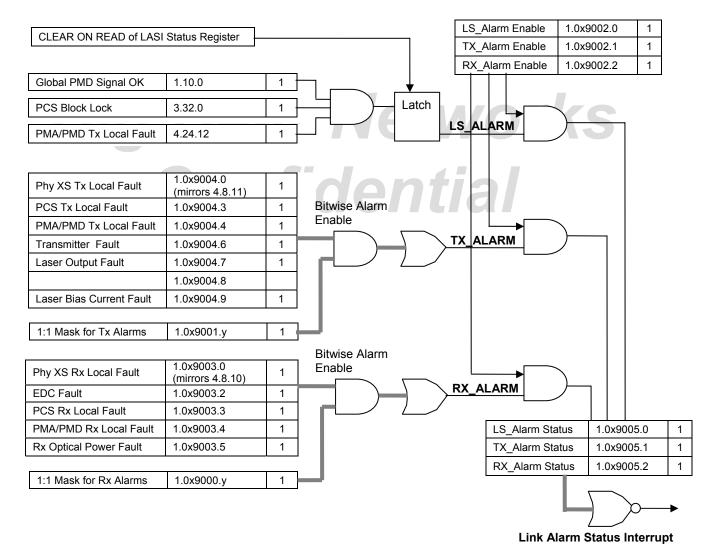

## Link Alarm Status Interrupt

Per the XENPAK MSA the Link Alarm Status Interrupt (LASI) pin is used to indicate a performance issue with either the transmit path or the receive path. LASI is the OR of the TX\_ALARM, the RX\_ALARM, and the LINK\_STATUS ALARM. The components contributing to these alarms are shown in the MDIO register list in Appendix A, specifically 0x9004, 0x9003 for the TX\_ALARM and RX\_ALARM. (The items contributing to the LINK\_STATUS alarm are listed at the end of the LASI section of Appendix A) The functionality of the LASI signal is shown below in Figure 4.

#### Latching

Most contributing components of the TX\_ALARM and RX\_ALARM are latching and are cleared only when that bit of the status register is read. The LS\_ALARM is latching and is asserted each time the LINK\_STATUS signal changes state. LS\_ALARM is cleared on a read of the LASI Status Register (1.0x9005).

#### Enabling and Masking

For the TX\_ALARM and the RX\_ALARM each of the contributing components can be independently enabled or disabled using the control registers 0x9001 and 0x9003. All three of the net TX, RX and LS alarms can be masked using the control register 0x9002 before the final OR function to produce the LASI signal.

Figure 4: Link Alarm Status Interrupt signal (LASI) Block Diagram

## Loop-back Modes

Five loop-back modes are supported in the Big Bear LRM-LR transponder. In a 'System Loop-back' the data on the transmit path is looped back into the receive path (see loops 1 to 3 below for PHY XS, PCS, and PMA system loop-backs). In 'Network Loop-back the data on the receive path is looped back into the transmit path (see loops 4 and 5 below for PHY XS Network Loop-back, and PMA Network Loop-back.)

#### Table 5: Loop-back Mode Details

|   | Loop-back<br>Mode           | Control<br>Register         | Description                                                                                                                                                                                                                                                                                                                                                                         | Bypassed<br>Path<br>Default<br>Output | Data Output<br>Enable<br>Register | Bypassed<br>Path Data<br>with Output<br>Enable =1 |

|---|-----------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------|---------------------------------------------------|

| 1 | XGXS<br>System<br>Loopback  | 4.49152.14<br>(4.0xC000.14) | Connects the XAUI 10B/8B<br>Decoder output to the XAUI<br>8B/10B encoder input.                                                                                                                                                                                                                                                                                                     | All 1's at<br>Optical Out             | 4.49152.15<br>(4.0xC000.15)       | Transmit Data at Optical Out                      |

| 2 | PCS<br>System<br>Loopback   | 3.0.14<br>(3.0x000.14)      | The PCS accepts data on the transmit path from the XGMII and returns it on the receive path to the XCMII. (802.3ae Clause 49.2.14.4)                                                                                                                                                                                                                                                | 0x00FF at<br>Optical Out              | 3.0.5<br>(3.0x000.5)              | Transmit Data<br>at Optical Out                   |

| 3 | PMA<br>System<br>Loopback   | 1.0.0<br>(1.0x000.0)        | When PMA system loop-back is<br>enabled then transmission<br>requests passed to the<br>transmitter are shunted directly<br>to the receiver, overriding any<br>signal detected by the receiver<br>on its attached link.<br>(802.3ae Clause 51.8)                                                                                                                                     | Transmit<br>Data at<br>Optical Out    | NA                                | NA                                                |

| 4 | XGXS<br>Network<br>Loopback | 4.0.14<br>(4.0x000.14)      | After the network data has<br>passed through the 8B/10B<br>encoder it is looped back to the<br>transmit side. Per 802.3ae<br>loopback applies to all lanes as<br>a group with lane 0 on the<br>receive chain looped back to<br>lane 0 on the transmit chain.<br>(Here transmit and receive are<br>defined relative to the optical<br>signal direction).<br>(802.3ae Clause 48.3.3). | Receive<br>Data to<br>RXDOUT          |                                   | NA                                                |

| 5 | PMA<br>Network<br>Loopback  | 1.49153.4<br>(1.0xC001.4)   | PMA Network Loop-back<br>returns the received optical<br>signal immediately following the<br>CDR to provide a retimed, de-<br>jittered signal to the output<br>driver of the Tx.                                                                                                                                                                                                    | Receive<br>Data to<br>RXDOUT          | 1.49153.9<br>(1.0xC001.9)         | ldle at<br>RXDOUT                                 |

## **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

#### Table 6 Absolute Maximum Ratings

| Rating                                      | Symbol           | Min  | Max  | Units |

|---------------------------------------------|------------------|------|------|-------|

| Storage Case Temperature                    | T <sub>stg</sub> | -40  | +85  | °C    |

| Receive Average Optical Input Power PIN     | P <sub>MAX</sub> |      | +4   | dBm   |

| +3.3V Supplies                              |                  | -0.3 | +3.6 | V     |

| +5.0V Supplies                              |                  | -0.3 | +6.0 | V     |

| APS Supplies                                |                  | -0.3 | +1.5 | V     |

| LV-CMOS Input Voltage                       |                  | -0.7 | 4.0  | V     |

| LV-CMOS Output Voltage                      |                  |      | 2.5  | V     |

| Static Discharge Voltage (Human Body Model) | ESD              |      | 2000 | V     |

| Relative Humidity (non-condensing)          | RH               | 15   | 90   | %     |

## **Recommended Operating Conditions**

Minimum and maximum values specified over operating case temperature range. Typical values are measured at room temperature unless otherwise noted.

| Table 7 Standard Operating Conditions |                  |            |       |         |       |           |  |  |

|---------------------------------------|------------------|------------|-------|---------|-------|-----------|--|--|

| Parameter                             | Name             | Conditions | Min   | Typical | Мах   | Units     |  |  |

| Operating Case Temperature            | Tc               |            | 0     |         | 70    | °C        |  |  |

| Transponder Power Consumption         | P <sub>DIS</sub> |            |       |         | 4     | W         |  |  |

| +3.3V Power Supply Voltage            | +3.3V            |            | 3.135 | 3.3     | 3.465 | V         |  |  |

| +5.0V Power Supply Voltage            | +5.0V            |            | 4.75  | 5.0     | 5.25  | V         |  |  |

| APS Power Supply Voltage              | APS              | Note 1.    | 1.21  | 1.25    | 1.29  | V         |  |  |

| +3.3V Power Supply Current            | 3.3V             |            |       |         | 1200  | mA        |  |  |

| +5.0V Power Supply Current            | 5.0V             |            |       |         | 0     | mA        |  |  |

| APS Power Supply Current              | APS              |            |       |         | 1000  | mA        |  |  |

| Ripple and Noise                      |                  |            |       |         | 40    | mV<br>rms |  |  |

Note 1: Required APS supply range is ± 3%

## Hot Swapping

The module can be hot-swapped.

#### Table 8 Turn-On Characteristics

| Parameter                         | Name                 | Conditions | Min | Typical | Мах  | Units   |

|-----------------------------------|----------------------|------------|-----|---------|------|---------|

| Peak Inrush Current               | I <sub>CC</sub> Peak |            |     |         | 0.75 | A / pin |

| Current Ramp Rate (for I < 100mA) | dl <sub>cc</sub> /dt |            |     |         | 50   | mA/ms   |

| Current Ramp Rate (for I > 100mA) | dl <sub>cc</sub> /dt | Note 1     |     |         | 100  | mA/ms   |

| Initialization Time               | T <sub>INIT</sub>    |            |     | TBD     | 5    | Seconds |

Note 1: Current step of 90mA during module initialization.

## **Optical Characteristics**

The Big Bear LRM-LR transponder meets the IEEE802.3aq D2.2 draft standard for LRM links and the IEEE standard for single mode 10km LR links.

The optical specifications are split into three groups:

- 1. Specifications common to LRM and LR which are either the same or where the worst case value is used.

- 2. Specifications pertaining to LRM performance only

- 3. Specifications pertaining to LR performance only.

All specifications are End Of Life.

| Parameter                                        | Symbol          | Conditions               | Min         | Typical       | Max         | Units    |

|--------------------------------------------------|-----------------|--------------------------|-------------|---------------|-------------|----------|

| Transmitter                                      |                 |                          |             |               |             |          |

| Center Wavelength                                | λc              |                          | 1260        |               | 1355        | nm       |

| Average Launch Power                             | Po              | (Note 1)<br>(Note 2)     | -6.5        |               | +0.5        | dBm      |

| Average Launch Power OFF                         |                 |                          |             |               | -30         | dBm      |

| Launch Power OMA                                 |                 | (Note 3)                 | -4.5        |               | +1.5        | dBm      |

| Extinction Ratio                                 | ER              |                          | 3.5         |               |             | dB       |

| RIN OMA                                          | 09              |                          |             |               | -128        | dBOMA/Hz |

| Optical Return Loss Tolerance                    | 50              |                          | FLVV        |               | 12          | dB       |

| Transmitter Reflectance                          |                 |                          |             |               | -12         | dB       |

| Eye Mask Margin                                  |                 |                          | 0           |               |             | %        |

| Transmitter Eye Mask<br>{X1, X2, X3, Y1, Y2, Y3} | DN              | (Note 4)<br>See Figure 6 | {0.25, 0.40 | , 0.45, 0.25, | 0.28, 0.40} |          |

| Receiver                                         |                 |                          |             |               |             |          |

| Nominal Center Wavelength                        | $\lambda_{NOM}$ |                          | 1260        |               | 1355        | nm       |

| Max Average Receive Power                        |                 | (Note 5)                 |             |               | 0.5         | dBm      |

| Receiver Reflectance                             |                 |                          |             |               | -12         | dB       |

#### Table 9: LRM-LR Transponder Optical Characteristics (Common to LRM and LR)

Notes:

1. Average Output Power (min) is informative only – a transmitter with power below this value cannot be compliant; however, a value above this does not ensure compliance.

2. The IEEE802.3aq D2.2 Minimum average launch power specification for LRM is the more restrictive and is the one used.

3. The IEEE802.3aq D2.2 Minimum launch power OMA for LRM is the more restrictive and is the one used. There is no max launch OMA specification for LR so the LRM value is used.

4. The transmit eye mask of the LR standard is more restrictive and is the one used (200 waveforms).

5. Maximum Average Receive Power is informative only.

##

## Table 10: LRM Specific Optical Characteristics

| Parameter                                      | Symbol | Conditions | Min  | Typical | Max   | Units |

|------------------------------------------------|--------|------------|------|---------|-------|-------|

| Transmitter                                    |        |            |      |         |       |       |

| RMS Spectral Width at 1260nm                   |        |            |      |         | 2.4   | nm    |

| RMS Spectral Width at 1300nm and 1355nm        |        |            |      |         | 4     | nm    |

| TWDP                                           |        | (Note 1)   |      |         | 4.7   | dB    |

| Uncorrelated Jitter                            |        |            |      |         | 0.033 | UI    |

| Encircled Flux in 5 micron radius              |        | (Note 2)   |      |         | 30    | %     |

| Encircled Flux in 11 micron radius             |        | (Note 2)   |      |         | 86    | %     |

| Receiver                                       |        |            |      |         |       |       |

| Overload Received Power (OMA)                  |        |            |      |         | 1.5   | dBm   |

| Min Received Power (OMA)                       |        | (Note 3)   | -6.5 |         |       | dBm   |

| Comprehensive Stressed<br>Receiver Sensitivity |        | (Note 4)   |      |         | -6.5  | dBm   |

| Simple Stressed Receiver<br>Sensitivity OMA    |        | (Note 5)   |      |         | -7.5  | dBm   |

| Jitter tolerance at 40KHz (p-p)                |        |            | 5    |         |       | UI    |

| Min Average receive power                      |        | (Note 6)   | -8.5 |         |       | dBm   |

Notes:

1. TWDP: Transmitter waveform and dispersion penalty. See IEEE802.3aq draft 2.2 for complete definition.

2. See IEEE802.3aq D2.2 Table 68-3? for detail of encircled flux specification

3. The Min Received Power (OMA) is informative only.

4. See Table 68.4? in the IEEE802.3aq D2.2 for details of the comprehensive stressed tests for TP3.

5. This test is informative only. See IEEE802.3aq D2.2 for detail on the simple stressed receiver sensitivity.

6. Minimum Average Receive Power is informative only – a received power below this value cannot be compliant; however, a value above this does not ensure compliance.

####

## Table 11: LR Specific Optical Characteristics

| Parameter                           | Symbol | Conditions | Min   | Typical | Max   | Units |

|-------------------------------------|--------|------------|-------|---------|-------|-------|

| Transmitter                         |        |            |       |         |       |       |

| Side Mode Suppression Ratio         |        |            |       |         | 30    | dB    |

| Transmitter Dispersion Penalty      |        |            |       |         | 3.2   | dB    |

| Launch OMA – TDP                    |        |            |       |         | -6.2  | dBm   |

| Receiver                            |        |            |       |         |       |       |

| Stressed Receiver Sensitivity (OMA) |        | (Note 1)   |       |         | -10.3 | dBm   |

| Max Receiver Sensitivity (OMA)      |        | (Note 2)   |       |         | -12.6 | dBm   |

| Stressed Eye Jitter                 |        |            | 0.3   |         |       | UI    |

| Min Average receive power           |        | (Note 3)   | -14.4 |         |       | dBm   |

| Vertical Eye Closure Penalty        |        |            | 2.2   |         |       | dB    |

| Receive 3dB upper cut off freq.     |        |            |       |         | 12.3  | GHz   |

Notes:

1. See Section 52.9.9.2 in the IEEE802.3ae for details of the LR stressed tests for TP3.

- 2. This is for the back-to-back condition and is informative only.

- 3. Minimum Average Receive Power is informative only a received power below this value cannot be compliant; however, a value above this does not ensure compliance.

Figure 6: Transmitter Eye Mask Definition (Per IEEE802.3ae sect 52.9.7)

## **Electrical Characteristics**

A X2 module will be functionally operational within 5 seconds of insertion. Parametric performance (such as laser line-width) may depend on thermal stabilization of the module and may take substantially longer and will depend on the thermal environment imposed by the host.

The XAUI electrical interface on the Big Bear Transponder complies fully with Clause 47 of IEEE802.3ae-2002.

#### Table 12: XAUI Input Interface

| Parameter                    | Symbol               | Conditions         | Min | Typical | Max  | Units |

|------------------------------|----------------------|--------------------|-----|---------|------|-------|

| Input Differential Voltage   | VIN DIFF             | p-p swing (Note 1) | 160 |         | 1600 | mV    |

| Differential Input Impedance | Z <sub>IN DIFF</sub> |                    | 80  |         | 120  | Ω     |

| Jitter tolerance             |                      | (Note 2)           |     |         |      |       |

Notes

1. The XAUI receiver successfully handles signals that meet the far-end eye mask per Section 47.3.3.5 of IEEE P802.3ae-2002.

2. The XAUI receiver meets sinusoidal jitter tolerance mask in figure 47-5 of IEEE P802.3ae-2002

#### Table 13: XAUI Driver Interface

| Parameter                     | Symbol                | Conditions                      | Min | Typical | Мах  | Units |

|-------------------------------|-----------------------|---------------------------------|-----|---------|------|-------|

| Output Differential Voltage   | V <sub>OUT DIFF</sub> | p-p swing (Note 1)              | 800 |         | 1600 | mV    |

| Differential Output Impedance | Z <sub>OUT DIFF</sub> | r Noti                          | 80  |         | 120  | Ω     |

| Rise and Fall times           | Tr, Tf                |                                 | 40  |         | 100  | ps    |

| Total Transmit Jitter         |                       | No Pre-equalization at near end |     |         | 0.35 | UI    |

| Notes                         |                       |                                 |     |         | •    |       |

1. The XAUI driver meets the near or far eye mask per Section 47.3.3.5 of IEEE P802.3ae-2002.

#### Table 14 LV-CMOS Input and Output Characteristics

| Parameter                  | Symbol            | Conditions                | Min  | Typical | Max    | Units |

|----------------------------|-------------------|---------------------------|------|---------|--------|-------|

| LV-CMOS Input DC Character | istics            |                           |      |         |        |       |

| Input High Voltage         | V <sub>IH</sub>   |                           | 0.84 |         | Note 1 | V     |

| Input Low Voltage          | VIL               |                           |      |         | 0.36   | V     |

| Input Pulldown Current     | I <sub>PD</sub>   | V <sub>IN</sub> =1.2V     | 20   | 40      | 120    | μA    |

| LV-CMOS Output DC Characte | eristics          | ·                         | •    |         |        |       |

| Output High Voltage        | V <sub>он</sub>   | I <sub>OH</sub> =-4mA     | 1.0  |         | 1.5    | V     |

| Output Low Voltage         | V <sub>OL</sub>   | I <sub>OL</sub> = 4mA     |      |         | 0.15   | V     |

| LV-CMOS AC Characteristics |                   | ·                         | •    |         |        |       |

| Rise Time                  | T <sub>RISE</sub> | C <sub>LOAD</sub> = 300pF |      |         | 30     | μs    |

| Fall Time                  | T <sub>FALL</sub> | C <sub>LOAD</sub> = 300pF |      |         | 50     | ns    |

Notes

1. Nominally 1.5V, but 3.3V Tolerant

# **BigBerrs**

## Table 15 MDIO Input and Output Characteristics

| Parameter                                   | Symbol          | Conditions               | Min  | Typical | Мах  | Units |

|---------------------------------------------|-----------------|--------------------------|------|---------|------|-------|

| MDIO Input DC Characteristics               |                 |                          |      |         |      |       |

| Input High Voltage                          | VIH             |                          | 0.84 |         | 1.5  | V     |

| Input Low Voltage                           | VIL             |                          | -0.3 |         | 0.36 | V     |

| MDIO Output DC Characteristics              |                 |                          |      |         |      |       |

| Output High Voltage                         | V <sub>OH</sub> | I <sub>он</sub> =-100 иА | 1.0  |         | 1.5  | V     |

| Output Low Voltage                          | Vol             | I <sub>OL</sub> = 100 uA | -0.3 |         | 0.2  | V     |

| Output High Current                         | I <sub>OL</sub> | V <sub>IN</sub> =0.3V    | -4   |         |      | mA    |

| MDIO AC Characteristics                     |                 |                          |      |         |      |       |

| Input Capacitance                           | Ci              |                          |      |         | 10   | pF    |

| MDIO Data Hold Time                         | Thold           |                          | 10   |         |      | ns    |

| MDIO Data Setup Time                        | Tsetup          |                          | 10   |         |      | ns    |

| Delay (MDC rising edge to MDIO data change) | Tdelay          |                          |      |         | 300  | ns    |

| MDC Clock Rate                              |                 |                          |      |         | 2.5  | Mb/s  |

Big Bear Networks Confidential

## **Electrical Connector**

The X2 transponder PCB forms the male half of the 70-way two row electrical connector and is designed to mate with TycoAMP Part 1367337-1 or Molex Part 74441-0003 or equivalent. The pin numbering and orientation on the transponder PCB are shown below in Figure 7.

Bottom of Transceiver PCB (as viewed through the top)

## **Electrical Pin-Out List**

The pin function definitions are provided in below. Note that pins 1-35 are constitute the lower row, while pins 36 -70 constitute the upper row.

| Pin # | Name          | Dir | Function                                                                                                         | Note |  |  |

|-------|---------------|-----|------------------------------------------------------------------------------------------------------------------|------|--|--|

| 1     | GND           |     | Electrical Ground                                                                                                |      |  |  |

| 2     | GND           |     | Electrical Ground                                                                                                |      |  |  |

| 3     | GND           |     | Electrical Ground                                                                                                |      |  |  |

| 4     | 5V            | I   | Power                                                                                                            |      |  |  |

| 5     | 3.3V          | I   | Power                                                                                                            |      |  |  |

| 6     | 3.3V          | I   | Power                                                                                                            |      |  |  |

| 7     | APS           | I   | Adaptive Power Supply (1.25V)                                                                                    |      |  |  |

| 8     | APS           | Ι   | Adaptive Power Supply (1.25V)                                                                                    |      |  |  |

| 9     | LASI          | 0   | Link Alarm Status Interrupt<br>High = Normal Operation<br>Low = LASI asserted<br>10K ohm pull-up on transponder. |      |  |  |

| 10    | BIG B         | -6  | Module Reset<br>High = Normal Operation<br>Low = Reset                                                           | S    |  |  |

| 11    | NOT CONNECTED |     |                                                                                                                  |      |  |  |

| 12    | Tx On/Off     |     | High = Transmitter On<br>Low = Transmitter Off<br>10K ohm pull-up on transponder.                                |      |  |  |

| 13    | NOT CONNECTED |     |                                                                                                                  |      |  |  |

| 14    | MOD DETECT    | 0   | Pulled low inside transponder through 1K Ohm                                                                     |      |  |  |

| 15    | NOT CONNECTED |     |                                                                                                                  |      |  |  |

| 16    | NOT CONNECTED |     |                                                                                                                  |      |  |  |

| 17    | MDIO          | I/O | Management Data I/O                                                                                              |      |  |  |

| 18    | MDC           | Ι   | Management Data Clock                                                                                            |      |  |  |

| 19    | PRTAD4        | I   | Port Address Bit 4                                                                                               |      |  |  |

| 20    | PRTAD3        | Ι   | Port Address Bit 3                                                                                               |      |  |  |

| 21    | PRTAD2        | Ι   | Port Address Bit 2                                                                                               |      |  |  |

| 22    | PRTAD1        | Ι   | Port Address Bit 1                                                                                               |      |  |  |

| 23    | PRTAD0        | Ι   | Port Address Bit 0                                                                                               |      |  |  |

| 24    | NOT CONNECTED | I   |                                                                                                                  |      |  |  |

| 25    | APS SET       | I   | Feedback input for APS                                                                                           |      |  |  |

| 26    | RESERVED      |     | Reserved for APD use                                                                                             |      |  |  |

| 27    | APS SENSE     | I   | APS Sense Connection                                                                                             |      |  |  |

| 28    | APS           | Ι   | Adaptive Power Supply (1.25V)                                                                                    |      |  |  |

| 29    | APS           | I   | Adaptive Power Supply (1.25V)                                                                                    |      |  |  |

| 30    | 3.3V          | Ι   | Power                                                                                                            |      |  |  |

| 3     | 3.3V          | I   | Power                                                                                                            |      |  |  |

| 32 | 5.0V       | 1 | Power                      |  |

|----|------------|---|----------------------------|--|

| 33 | GND        |   | Electrical Ground          |  |

| 34 | GND        |   | Electrical Ground          |  |

| 35 | GND        |   | Electrical Ground          |  |

| 36 | GND        |   | Electrical Ground          |  |

| 37 | GND        |   | Electrical Ground          |  |

| 38 | RESERVED   |   |                            |  |

| 39 | RESERVED   |   |                            |  |

| 40 | GND        |   | Electrical Ground          |  |

| 41 | RX LANE 0+ | 0 | Module XAUI Output Lane 0+ |  |

| 42 | RX LANE 0- | 0 | Module XAUI Output Lane 0- |  |

| 43 | GND        |   | Electrical Ground          |  |

| 44 | RX LANE 1+ | 0 | Module XAUI Output Lane 1+ |  |

| 45 | RX LANE 1- | 0 | Module XAUI Output Lane 1- |  |

| 46 | GND        |   | Electrical Ground          |  |

| 47 | RX LANE 2+ | 0 | Module XAUI Output Lane 2+ |  |

| 48 | RX LANE 2- | 0 | Module XAUI Output Lane 2- |  |

| 49 | GND        |   | Electrical Ground          |  |

| 50 | RX LANE 3+ | 0 | Module XAUI Output Lane 3+ |  |

| 51 | RX LANE 3- | 0 | Module XAUI Output Lane 3- |  |

| 52 | GND        |   | Electrical Ground          |  |

| 53 | GND        |   | Electrical Ground          |  |

| 54 | GND        |   | Electrical Ground          |  |

| 55 | TX LANE 0+ | 0 | Module XAUI Input Lane 0+  |  |

| 56 | TX LANE 0- | 0 | Module XAUI Input Lane 0-  |  |

| 57 | GND        |   | Electrical Ground          |  |

| 58 | TX LANE 1+ | 0 | Module XAUI Input Lane 1+  |  |

| 59 | TX LANE 1- | 0 | Module XAUI Input Lane 1-  |  |

| 60 | GND        |   | Electrical Ground          |  |

| 61 | TX LANE 2+ | 0 | Module XAUI Input Lane 2+  |  |

| 62 | TX LANE 2- | 0 | Module XAUI Input Lane 2-  |  |

| 63 | GND        |   | Electrical Ground          |  |

| 64 | TX LANE 3+ | 0 | Module XAUI Input Lane 3+  |  |

| 65 | TX LANE 3- | 0 | Module XAUI Input Lane 3-  |  |

| 66 | GND        |   | Electrical Ground          |  |

| 67 | RESERVED   |   |                            |  |

| 68 | RESERVED   |   |                            |  |

| 69 | GND        |   | Electrical Ground          |  |

| 70 | GND        |   | Electrical Ground          |  |

## Package Outline Diagram

## Table 17 Mechanical Dimensions

| Parameter                    | Notes  | Value (inches)       | Value (mm) |  |

|------------------------------|--------|----------------------|------------|--|

| A                            | Note 1 |                      | 39.6       |  |

| В                            | Note 1 |                      | 12.0       |  |

| С                            | Note 1 |                      | 11.0       |  |

| Type of electrical interface |        | XAUI                 |            |  |

| Type of optical interface    | Note 2 | SC Duplex Receptacle |            |  |

Note 1: Mechanical dimensions conform to Section 6.8 of X2 MSA Rev 1.0

Note 2: Per section 6.16 of X2 MSA Rev 1.0

Figure 8 Transponder Mechanical Drawing

#### NOTE: THE X2 TRANSPONDER IS ALSO AVAILABLE IN THE MID AND TALL HEAT SINK FORMATS

## Safety

The transponder is classified as a Class I laser product per IEC 60825-1 and pre CFR 21 part 1040.10

## **Reliability and Qualification**

To ensure high product reliability and customer satisfaction, Big Bear Networks has developed a comprehensive Quality and Reliability program. All Transponders are qualified to Big Bear Networks internal standards using MIL-STD-883 test methods and procedures and sampling techniques consistent with Telcordia Technologies requirements. This program characterizes and qualifies components and products starting at the design phase, and on-going through the manufacturing process. The qualification test requirements are designed based on the following industry standards:

Transponders subassemblies based on GR-468 (opto-electronic devices)

Contact Big Bear Networks for the latest information on our product qualification plans and reliability specifications.

## References

The following references are provided for informational purposes only. The parameters and operational behavior outlined in this specification describe the complete functionality of the 10G Transponder. Contact Big Bear Networks for any items concerning the operational characteristics of this device.

dential

- 1. IEEE 802.3ae-2002, August 30, 2002.

- 2. Draft IEEE 802.3aq D2.2 , August 2005

- 3. XENPAK MSA Rev 3.0, September 18, 2002

- 4. X2 MSA Rev 1.0, January 30, 2003.

## Appendix A: MDIO Registers

The transponder adheres to the general specification for the MDIO interface given in Clause 45 of IEEE P802.3ae-2002.

Note that the MDIO register functionality is taken from the following source documents:

- PMA/PMD Registers 0x0000 to 0x000F are taken from IEEE802.3ae section 45.2.1

- PMA/PMD Registers 0x8000 to 0x8FFF are taken from XENPAK MSA 3.0 section 10.8 10.12

- The LASI Section 0x9000 to 0x9005 is taken from XENPAK MSA 3.0 section 10.13

- PCS Registers 0x0000 to 0xFFFF are taken from IEEE802.3ae section 45.2.3

- PHY XS Registers 0x0000 to 0xFFFF are taken from IEEE802.3ae section 45.2.4

| Device | PMA/PMD Register<br>(Decimal) | PMA/PMD Register<br>(Hex) | Register Name                            |

|--------|-------------------------------|---------------------------|------------------------------------------|

| 1      | 0                             |                           | PMA/PMD Control 1                        |

| 1      | 1                             |                           | PMA/PMD Status 1                         |

| 1      | 2-3                           |                           | Device Identifier                        |

| 1      |                               |                           | PMA/PMD Speed Ability                    |

| 1      | 5-6                           |                           | Devices in Package                       |

| 1      | 7                             |                           | 10G PMA/PMD Control 2                    |

| 1      | 8                             | ntia                      | 10G PMA/PMD Status 2                     |

| 1      | 9                             | JIIIU                     | 10G PMD transmit disable                 |

| 1      | 10                            |                           | 10G PMD receive signal detect            |

| 1      | 14-15                         |                           | Package Identifier                       |

| 1      | 32768                         | 8000                      | NVR Control/Status                       |

| 1      | 32775                         | 8007                      | XENPAK MSA supported                     |

| 1      | 32776-32777                   | 8008 - 8009               | NVR size in bytes                        |

| 1      | 32778-32778                   | 800A-800B                 | Number of bytes used                     |

| 1      | 32780                         | 800C                      | Basic Field Address                      |

| 1      | 32781                         | 800D                      | Customer Field Address                   |

| 1      | 32782                         | 800E                      | Vendor Field Address                     |

| 1      | 32783 - 32784                 | 800F-8010                 | Extended Vendor Field Address            |

| 1      | 32785                         | 8011                      | Reserved                                 |

| 1      | 32786                         | 8012                      | Transceiver Type                         |

| 1      | 32787                         | 8013                      | Optical Connector Type                   |

| 1      | 32787                         | 8014                      | Bit Encoding                             |

| 1      | 32789-32790                   | 8015 - 8016               | Nominal Bit Rate (in multiples of 1Mb/s) |

| 1      | 32791                         | 8017                      | Protocol Type                            |

## **Device 1 PMA/PMD Registers**

| Device | PMA/PMD Register<br>(Decimal) | PMA/PMD Register<br>(Hex) | Register Name                                          |  |  |

|--------|-------------------------------|---------------------------|--------------------------------------------------------|--|--|

| 1      | 32792-32801                   | 8018 - 8021               | Standards Compliance Codes 10GbE Code Byte 0           |  |  |

| 1      | 32802-32803                   | 8022 - 8023               | Specified Transmission Range (In 10m Increments)       |  |  |

| 1      | 32804-32805                   | 8024 – 8025               | Fiber type Byte 0 and Byte 1                           |  |  |

| 1      | 32806 - 32808                 | 8026 – 8028               | Center Optical Wavelength(in 0.01nm steps - Channel 0) |  |  |

| 1      | 32818 - 32821                 | 8032 - 8035               | Package Identifier OUI                                 |  |  |

| 1      | 32822-32825                   | 8036 - 8039               | Transceiver Vendor OUI                                 |  |  |

| 1      | 32826-32841                   | 803A – 8049               | Transceiver Vendor name in ASCII                       |  |  |

| 1      | 32842-32875                   | 804A – 8059               | Part number provided by Transceiver vendor in ASCII    |  |  |

| 1      | 32858-32859                   | 805A – 805B               | Revision level for part - provided by Vendor (ASCII)   |  |  |

| 1      | 32860-32875                   | 805C – 806B               | Vendor Serial Number in ASCII                          |  |  |

| 1      | 32876-32885                   | 806C - 8075               | Vendor manufacturing date code in ASCII                |  |  |

| 1      | 32886                         | 8076                      | 5V stressed environmental reference                    |  |  |

| 1      | 32887                         | 8077                      | 3.3V stressed environmental reference                  |  |  |

| 1      | 32888                         | 8078                      | APS stressed environment reference                     |  |  |

| 1      | 32889                         | 8079                      | Nominal APS voltage                                    |  |  |

| 1      | 32890                         | 807A                      | DOM Capability                                         |  |  |

| 1      | 32891                         | 807B                      | Reserved                                               |  |  |

| 1      | 32893                         | 807D                      | Basic Field Checksum                                   |  |  |

| 1      | 32894-32941                   | 807E – 80AD               | Customer writable area                                 |  |  |

| 1      | 32942-33030                   | 80AE - 8106               | Vendor Specific                                        |  |  |

| 1      | 33031-36863                   | 8107 – 8FFF               | Extended Vendor Specific                               |  |  |

| 1      | 36864                         | 9000                      | RX_ALARM Control                                       |  |  |

| 1      | 36865                         | 9001                      | TX_ALARM Control                                       |  |  |

| 1      | 36866                         | 9002                      | LASI Control                                           |  |  |

| 1      | 36867                         | 9003                      | RX_ALARM Status                                        |  |  |

| 1      | 36868                         | 9004                      | TX_ALARM Status                                        |  |  |

| 1      | 36869                         | 9005                      | LASI Status                                            |  |  |

| 1      | 49153                         | C001                      | Extended PMA Features                                  |  |  |

| 1      | 49155                         | C003                      | PMA/PMD Vendor Specific                                |  |  |

| 1      | 49156                         | C004                      | PMA/PMD Vendor Specific Checksum                       |  |  |

| 1      | 49188                         | C024                      | PMA Vendor Specific                                    |  |  |

#### Register 1.0 (0x0000) – PMA/PMD Control

| Bit      | Name            | Description                                         | R/W | Default |

|----------|-----------------|-----------------------------------------------------|-----|---------|

| 1.0.15   | Reset           | 1= PMA/PMD reset                                    | RW  | 0       |

|          |                 | 0 = normal operation                                |     |         |

|          |                 | Sets all PMA/PMD registers to their default states. |     |         |

| 1.0.14   | Reserved        | Value always 0, writes ignored                      | RW  | 0       |

| 1.0.13   | Speed Selection | 1= Operation at 10Gb/s and above                    | RW  | 1       |

|          |                 | 0 = Unspecified                                     |     |         |

|          |                 | NOTE 1                                              |     |         |

| 1.0.12   | Reserved        | Value always 0, writes ignored                      | RW  | 0       |

| 1.0.11   | Low Power       | 1 = Low power mode                                  | RW  | 0       |

|          |                 | 0 = Normal operation                                |     |         |

| 1.0.10:7 | Reserved        | Value always 0, writes ignored                      | RW  | 0       |

| 1.0.6    | Speed Selection | 1 = Operation at 10Gb/s and above                   | RW  | 1       |

|          |                 | 0 = Unspecified                                     |     |         |

|          |                 | NOTE 1                                              |     |         |

| 1.0.5:2  | Speed Selection | 5432                                                | RW  | 0000    |

|          |                 | 1 x x x = Reserved                                  |     |         |

|          |                 | x 1 x x = Reserved                                  |     |         |

|          |                 | x x 1 x = Reserved                                  |     |         |

|          |                 | 0 0 0 1 = Reserved                                  |     |         |

|          |                 | 0 0 0 0 = 10Gb/s                                    |     |         |

| 1.0.1    | Reserved        | Value always 0, writes ignored                      | RW  | 0       |

| 1.0.0    | PMA Loopback    | 1=Enable PMA loopback                               | RW  | 0       |

|          |                 | 0=Disable PMA loopback                              |     |         |

Note 1: Bits 6 and 13 both need to be set to '1'. These locations were previously used by Clause 22 to set the speed of devices running at speeds of 1Gb/s and below. Register 1.1 (0x0001) – PMA/PMD Status 1

| Bit      | Name                   | Description                                                                                                                                                                                        | R/W   | Default |

|----------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|

| 1.1.15:8 | Reserved               | NA                                                                                                                                                                                                 | RO    | NA      |

| 1.1.7    | Fault                  | 1 = Local fault condition detected in PMA/PMD<br>0 = Local fault condition not detected in PMA/PMD<br>Alarm = TX Local Fault or RX Local Fault (i.e. when<br>either 1.8.11 or 1.8.10 are set high) | RO    | 0       |

| 1.1.6:3  | Reserved               | NA                                                                                                                                                                                                 | RO/LL | NA      |

| 1.1.2    | Receive Link<br>Status | 1 = PMA locked to receive signal<br>0 = PMA not locked to receive signal                                                                                                                           | RO/LL | 1       |

| 1.1.1    | Power down ability     | 1 = PMA/PMD supports low power mode<br>0 = PMA/PMD does not support low power mode                                                                                                                 | RO    | ??      |

| 1.1.0    | Reserved               | NA                                                                                                                                                                                                 |       | NA      |

#### Register 1.2 to 1.3 (0x0002 – 0x0003) – Device Identifier

| Bit                                                                                                              | Name           | Description | R/W | Default |  |

|------------------------------------------------------------------------------------------------------------------|----------------|-------------|-----|---------|--|

| 1.3.15:0                                                                                                         | PMA Identifier |             | RO  |         |  |

| 1.2.15:0                                                                                                         | PMA Identifier |             | RO  |         |  |

| These registers enable the provision of a unique identifier for a particular type of DMA/DMD see IEEE802 3ae for |                |             |     |         |  |

These registers enable the provision of a unique identifier for a particular type of PMA/PMD – see IEEE802.3ae for further detail. Currently Big Bear fills these registers with all zero bits.

### Register 1.4 (0x0004) – PMA/PMD Speed Ability

| Bit      | Name              | Description                                                                                        | R/W | Default |

|----------|-------------------|----------------------------------------------------------------------------------------------------|-----|---------|

| 1.4.15:1 | Reserved (future) |                                                                                                    | RO  | 0       |

| 1.4.0    | 10G Capable       | 1 = PMA/PMD is capable of operating at 10Gb/s<br>0 = PMA/PMD is not capable of operating at 10Gb/s | RO  | 1       |

## Register 1.5 to 1.6 (0x0005 – 0x0006) – PMA/PMD Devices in Package

| Bit      | Name              | Description                                         | R/W | Default |

|----------|-------------------|-----------------------------------------------------|-----|---------|

| 1.6.15   | Vendor Specific   | 1 = Vendor specific device 2 present                | RO  | Delault |

| 1.0.15   | Device 2 present  | 0 = Vendor specific device 2 present in package     | R0  | 0       |

| 1.6.14   | Vendor Specific   | 1 = Vendor specific device 1 present                | RO  | 1       |

|          | Device 1 present  | 0 = Vendor specific device 1 not present in package |     |         |

| 1.6.13:0 | Reserved          | N/A                                                 | RO  |         |

| 1.5.15:6 | Reserved          | N/A                                                 | RO  |         |

| 1.5.5    | DTE XS Present    | 1 = DTE XS present in package                       | RO  | 0       |

|          |                   | 0 = DTE XS not present in package                   |     |         |

| 1.5.4    | PHY XS Present    | 1 = PHY XS present in package                       | RO  | 1       |

|          |                   | 0 = PHY XS not present in package                   |     |         |

| 1.5.3    | PCS Present       | 1 = PCS present in package                          | RO  | 1       |

|          |                   | 0 = PCS not present in package                      |     |         |

| 1.5.2    | WIS Present       | 1 = WIS present in package                          | RO  | 0       |

|          |                   | 0 = WIS not present in package                      |     |         |

| 1.5.1    | PMA/PMD           | 1 = PMA/PMD present in package                      | RO  | 1       |

|          | Present           | 0 = PMA/PMD not present in package                  |     |         |

| 1.5.0    | Clause 22         | 1 = Clause 22 registers present in package          | RO  | 0       |

|          | Registers present | 0 = Clause 22 registers not present in package      |     |         |

## Register 1.7 (0x0007) – 10G PMA/PMD Control 2

| Bit      | Name         | Description                      | R/W | Default |

|----------|--------------|----------------------------------|-----|---------|

| 1.7.15:4 | Reserved     | Value always 0, writes ignored   | R/W | -0      |

| 1.7.3:0  | PMA/PMD type | 3210                             | R/W | 1000    |

|          | selection    | 11XX Reserved                    |     |         |

|          |              | 101X Reserved                    |     |         |

|          |              | 1 0 0 0 10GBASE-LRM              |     |         |

|          |              | 0 1 1 1 10GBASE-SR PMA/PMD type  |     |         |

|          |              | 0 1 1 0 10GBASE-LR PMA/PMD type  |     |         |

|          |              | 0 1 0 1 10GBASE-ER PMA/PMD type  |     |         |

|          |              | 0 1 0 0 10GBASE-LX4 PMA/PMD type |     |         |

|          |              | 0 0 1 1 10GBASE-SW PMA/PMD type  |     |         |

|          |              | 0 0 1 0 10GBASE-LW PMA/PMD type  |     |         |

|          |              | 0 0 0 1 10GBASE-EW PMA/PMD type  |     |         |

|          |              | 0 0 0 0 10GBASE-CX4 PMA/PMD type |     |         |

## Register 1.8 (0x0008) – 10G PMA/PMD Status 2

| Bit       | Name                         | Description                                                                                                                                                                      | R/W   | Default |

|-----------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|

| 1.8.15:14 | Device Present               | 151410= Device responding at this address11= No device responding at this address01= No device responding at this address00= No device responding at this address                | RO    | 10      |

| 1.8.13    | Transmit fault<br>ability    | 1 = PMA/PMD has the ability to detect a fault<br>condition on the transmit path<br>0 = PMA/PMD does not have the ability to detect a<br>fault condition on the transmit path     | RO    | 1       |

| 1.8.12    | Receive Fault<br>ability     | 1 = PMA/PMD has the ability to detect a fault<br>condition on the receive path<br>0 = PMA/PMD does not have the ability to detect a<br>fault condition on the receive path       | RO    | 1       |

| 1.8.11    | Transmit Fault               | 1 = Fault condition on the transmit path<br>0 = No Fault condition on the transmit path<br>Transmit Fault = Tx PLL loss of lock + Laser Bias<br>Alarm + Laser Output Power Alarm | RO/LH | 0       |

| 1.8.10    | Receive Fault                | 1 = Fault condition on the receive path<br>0 = No Fault condition on the receive path<br>Receive Fault = RXLoS + Rx PLL loss of lock + EDC<br>PLL loss of lock.                  | RO/LH | 0       |

| 1.8.9     | Reserved                     | Ignore on read                                                                                                                                                                   |       | C       |

| 1.8.8     | PMD transmit disable ability | <ul> <li>1 = PMD has the ability to disable the transmit path</li> <li>0 = PMD does not have the ability to disable the transmit path</li> </ul>                                 | RO    | 51      |

| 1.8.7     | 10GBASE-SR<br>Ability        | 1 = PMA/PMD is able to perform 10GBASE –SR<br>0 = PMA/PMD is not able to performe 10GBASE-SR                                                                                     | RO    | 0       |

| 1.8.6     | 10GBASE-LR<br>Ability        | 1 = PMA/PMD is able to perform 10GBASE –LR<br>0 = PMA/PMD is not able to performe 10GBASE-LR                                                                                     | RO    | 1       |

| 1.8.5     | 10GBASE-ER<br>Ability        | 1 = PMA/PMD is able to perform 10GBASE –ER<br>0 = PMA/PMD is not able to performe 10GBASE-ER                                                                                     | RO    | 0       |

| 1.8.4     | 10GBASE-LX4<br>Ability       | 1 = PMA/PMD is able to perform 10GBASE –LX4<br>0 = PMA/PMD is not able to performe 10GBASE-LX4                                                                                   | RO    | 0       |

| 1.8.3     | 10GBASE-SW<br>Ability        | 1 = PMA/PMD is able to perform 10GBASE –SW<br>0 = PMA/PMD is not able to performe 10GBASE-SW                                                                                     | RO    | 0       |

| 1.8.2     | 10GBASE-LW<br>Ability        | 1 = PMA/PMD is able to perform 10GBASE –LW<br>0 = PMA/PMD is not able to performe 10GBASE-LW                                                                                     | RO    | 0       |

| 1.8.1     | 10GBASE-EW<br>Ability        | 1 = PMA/PMD is able to perform 10GBASE –EW<br>0 = PMA/PMD is not able to performe 10GBASE-EW                                                                                     | RO    | 0       |

| 1.8.0     | PMA Loopback<br>ability      | <ul> <li>1 = PMA has the ability to perform a loopback function</li> <li>0 = PMA does not have the ability to perform a loopback function</li> </ul>                             | RO    | 1       |

#### Register 1.9 (0x0009) – 10G PMD Transmit Disable

| Bit      | Name             | Description                    | R/W | Default |

|----------|------------------|--------------------------------|-----|---------|

| 1.9.15:5 | Reserved         | Value always 0, writes ignored | R/W | 0       |

| 1.9.4:1  | Not Used         | (Used for LX4 Only)            | R/W | 0       |

| 1.9.0    | Global PMD       | 1 = Disable transmitter output | R/W | 0       |

|          | Transmit Disable | 0 = Enable transmitter output  |     |         |

## Register 1.10 (0x000A) – 10G PMD Receive Signal Detect

| Bit       | Name           | Description                         | R/W | Default |

|-----------|----------------|-------------------------------------|-----|---------|

| 1.10.15:5 | Reserved       | Value always 0, writes ignored      | RO  | 0       |

| 1.10.4:1  | Not Used       | (Used for LX4 Only)                 | RO  | 0       |

| 1.10.0    | Global PMD     | 1 = Signal detected on receiver     | RO  | 1       |

|           | receive signal | 0 = Signal not detected on receiver |     |         |

|           | detect         | Alarm = RX LoS < $-15 \pm 1.1$ dBm  |     |         |

#### Register 1.11 (0x000B) – 10G PMA/PMD Extended Ability register bit definitions

| Bit       | Name                   | Description                                                                                  | R/W | Default       |

|-----------|------------------------|----------------------------------------------------------------------------------------------|-----|---------------|

| 1.11.15:3 | Reserved               | Ignore on Read                                                                               | RO  |               |

| 1.11.1    | 10GBASE-LRM<br>Ability | 1 = PMA/PMD is able to perform 10GBASE-LRM<br>0 = PMA/PMD is not able to perform 10GBASE-LRM | RO  | 0<br>(Note 1) |

| 1.11.0    | 10GBASE-CX4<br>Ability | 1 = PMA/PMD is able to perform 10GBASE-CX4<br>0 = PMA/PMD is not able to perform 10GBASE-CX4 | RO  | 0             |

Note 1: The current PMA does not support this new register at this point in time and will return a 0 in this field.

#### Registers 1.14 – 1.15 (0x000E-0x000F) – PMA/PMD package identifier

Registers 1.14 and 1.15 provide a 32 bit value, which may constitute a unique identifier for a particular type of package that the PMA/PMD is instantiated with. The identifier shall be composed of the third through 24<sup>th</sup> bits of the Organizationally Unique Identifier (OUI) assigned to the package manufacturer by the IEEE, plus a six bit model number, plus a four-bit revision number.

NOTE that these two registers completely duplicate the values in registers 1.8032h thru 1.8035h and the mapping is shown here.

| Bit     | Name               | Value     | Bit     | Name               | Value     |

|---------|--------------------|-----------|---------|--------------------|-----------|

| 1.15.15 | Package Identifier | 1.8032h.7 | 1.14.15 | Package Identifier | 1.8034h.7 |

| 1.15.14 | Package Identifier | 1.8032h.6 | 1.14.14 | Package Identifier | 1.8034h.6 |

| 1.15.13 | Package Identifier | 1.8032h.5 | 1.14.13 | Package Identifier | 1.8034h.5 |

| 1.15.12 | Package Identifier | 1.8032h.4 | 1.14.12 | Package Identifier | 1.8034h.4 |