# Kodiak OC-768 / STM-256 Short Reach 40Gb/s Electro-Optical Transponder (BBTR4005) (with integrated Clock & Data Recovery, Clock Synthesis and Multiplexer / Demultiplexer)

Preliminary Specifications (updated 7/9/2003) Rev 0.99e Contact <u>support@bigbearnetworks.com</u> for support

# Features

- Electro-optical transponder operating at 40 Gb/s

- Supports OC-768 SONET and STM-256 SDH

- 16-channel 2.488 Gb/s mux /demux

- Integrated Clock Multiplication Unit

- High-performance 40Gb/s Clock & Data Recovery

- High-performance photo-receiver

- 1.5um CW Laser Source (C-band compatible)

- Optimized Modulator & Driver

- Common form factor for short reach, intermediate reach and long reach applications

- Internal protection permits any power-up sequence

- Extensive Control and Monitoring Capabilities

- Transmit & Receive Monitors

- Transmitter Laser Disable Input

- Operates with Standard Supply Voltages

- Compatible with Applicable Industry Standards

- OIF-SFI5-01.0 / OIF-SXI5-01.0

- ITU G.693, 2km links (VSR2000-3R2, 3R3 & 3R5)

- ITU G.8251

# Applications

- Cross-office Telecommunication & High-speed Data Communication Applications

- Metropolitan & Regional Area Networks, Inter- / Intra-office SONET/SDH Systems /

# **General Description**

The Kodiak transponder performs the complete parallel electrical to serial optical conversion along with the required highspeed clock generation, clock and data recovery and associated 'care and feeding' of the electro-optical components. System designers are freed from the ultra-high speed design challenges of the 40Gb/s interface. The transponder offers the highest level of integration with the industry's smallest form factor package for a complete 40Gb/s interface, making it an ideal solution for time-to-market design strategies for telecommunication applications. The electrical data interface consists of 16 differential lines of data at 2.488 Gb/s for both transmit and receive directions. The optical interface consists of a 39.813 Gb/s optical bit-stream that can transport through lengths up to 2 km of single-mode fiber.

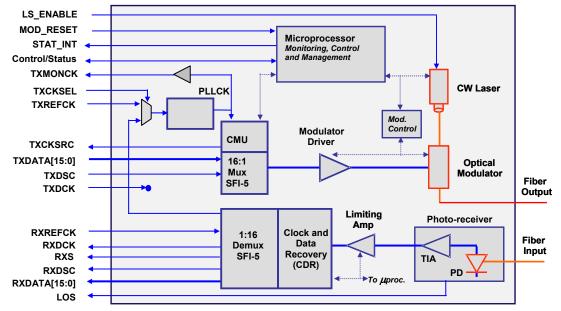

Figure 1 Transponder Block Diagram

# **Block Diagram Description**

Figure 1 depicts a simplified block diagram of the Kodiak transponder. This bi-directional device provides a SONET/SDH compliant electro-optical interface between an OC-768/STM-256 optical signal and the electrical physical layer. The transponder operates at the standard SONET/SDH rate of 39.81Gb/s. The transponder contains a 40Gb/s optical transmitter and a 40Gb/s optical receiver, as well as the electronics required to multiplex and de-multiplex sixteen 2.488Gb/s electrical channels. Clock multiplication, clock and data recovery, and channel de-skew / alignment circuitry are embedded within the transponder.

In the transmit direction, sixteen electrical CML data channels at 2.488Gb/s are multiplexed into an optical signal at 39.813Gb/s, then launched onto an attached optical fiber pigtail. An internal reference signal at the operating rate (39.813GHz) is phase-locked to an external data timing reference clock, operating at either 1/64 or 1/16 of the operating rate, i.e. 622 MHz, or 2.488 GHz. The optical transmitter is provided by a 1.5um cooled DFB laser. The optical output signal is SONET and ITU compliant for OC-768/STM-256 applications to the extent that the respective industry specifications have been completed.

In the receive direction, the transponder receives a 39.813Gb/s optical signal, converts it to an electrical signal, extracts a clock then de-multiplexes the data into sixteen differential CML data channels at 2.488Gb/s. The optical receiver utilizes an InGaAs/InP PIN photo-detector and high performance trans-impedance amplifier.

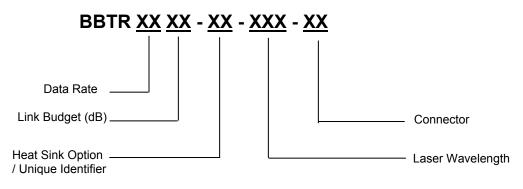

# Kodiak Transponder Product Line

The optical transmitter parameters of the Kodiak transponder are optimized for the particular SDH/SONET link characteristics in which it is to operate. Three distinct span lengths can be accommodated within the Kodiak product family (nominally 2km, 40km and 80km), providing a single active device footprint for accommodating applications ranging from intra-office at 2km to regional-based interconnects at 80km. This specification covers the short reach (SR) Kodiak Transponder operating at the standard 'non-FEC' rate of 39.8131 Gb/s. Contact Big Bear Networks for a detailed set of specifications and availability information for Transponders targeted at other operating distances and rates.

# **Functional Description**

# Transmitter

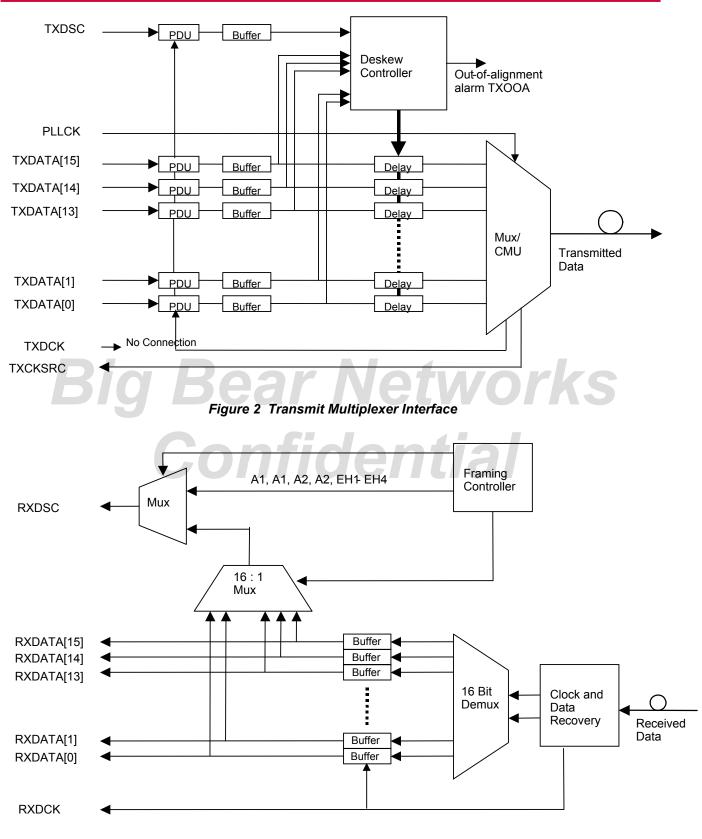

The high-speed multiplexer block shown in

*Figure* 1 and *Figure* 2 latches the data from the sixteen 2.488 Gb/s channels, provides the channel de-skew functions, and performs the required parallel-to-serial conversion. The FIFO input latches the data from the TXDATA\_P/N [15:0]. Refer below for a detailed treatment of the Transponder / SONET Framer Interface functionality. The serialized data is shifted out of the high-speed multiplexer at the transmit serial clock rate of 39.813 Gb/s to the optical modulator driver.

The ultra-high speed modulator driver provides amplification of the 39.813 Gb/s signal to the high-drive levels required by the optical modulator. The characteristics and capabilities of the driver are matched to the particular optical modulator embedded within the Kodiak Transponder to achieve optimum transmitter performance.

The integrated electro-optic modulator imposes the 40 Gb/s data signal onto CW light from a single mode semiconductor laser. The modulator is specifically designed for the 1550nm window, external amplitude modulation application of the 40G Kodiak transponder. The transmitter has a cooled DFB laser as the optical element and operates nominally in the 1530 – 1565 nm range.

#### Receiver

The optical receiver of the Kodiak transponder has a high-speed InGaAs/InP PIN photo-detector and a wideband trans-impedance amplifier (TIA), which are optimized for the particular fiber link characteristics in which it was designed to operate. The receiver converts the incident optical power to a photocurrent via the highperformance PIN photo-detector. The detected serial data output of the Kodiak receiver is connected to a limiting amplifier / clock and data recovery (CDR) subassembly, which extracts the 39.813 GHz clock signal and recovers the data stream.

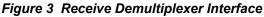

This recovered serial bit clock signal and the retimed serial data signals are presented to the 16-bit demultiplexer, which performs the serial-to-parallel conversion and interface functionality required for the system-side device. Refer to the Transponder / SONET Framer Interface section below for specific functional characteristics of this interface block.

## Transponder / SONET Framer Interface

The following functional description provides the details of the 16-bit interface from the system-side ASIC device (typically a SONET/SDH framer) to the Kodiak Transponder. The Kodiak transponder complies with the Optical Internetworking Forum (OIF) Physical & Link Layer SFI-5 and SxI-5 interface implementation specification documents.

Figure 2 below shows a logical model of the Transmit interface in the Kodiak Transponder. Data on the Transmit Data bus (TXDATA[15:0]) is conditioned by the Phase Detector Units (PDU), which tracks the center of

the "eye" for each bit. Data from each bit lane is written into an associated re-timing buffer. Data from the retiming buffer associated with TXDATA[15] is transmitted first onto the fiber while data that is associated with TXDATA [0] is transmitted last. The re-timing buffers acts as a set of FIFOs to bridge between the Transmit interface timing domain and the optical Transmit timing domain. The re-timing buffers absorb the allowed skew between the bit lanes.

The Kodiak Transponder monitors the Transmit Deskew Channel (TXDSC) for the reference data sourced by the It adjusts the delay of each system-side ASIC. TXDATA[15:0] signal, on a unit interval by unit interval basis, such that the delay from source device to the output of the re-timing buffers at the Transponder is identical for all 16 TXDATA signals. When the skew of all 16 data channels is compensated and locked, the TX OOA alarm is removed. The Deskew algorithm continues to operate after the TX OOA is removed. Under normal circumstances, the interface operates continuously with skew being monitored, and the TX OOA alarm remains off. If failure of the Deskew algorithm occurs, and any of the 16 channels fall out of lock, then the TX OOA alarm is enabled. TX OOA is an I<sup>2</sup>C alarm.

The function of the Deskew Controller block is to recognize the framing bytes and header bytes in the Deskew Channel TXDSC, to identify the start of the reference data that is replicated from each of TXDATA[X]. Each of the TXDATA[X] channels is then compared with the sampled data in the Deskew Channel in turn. The Deskew Controller performs a pattern match between the replicated data in TXDSC with the original data in the corresponding TXDATA[X] signal. Where there is a match, the relative delay of TXDATA[x], in relation to TXDSC, is found. It is possible to measure how many bit periods of skew there are on each channel. This information is used to compensate for the skew by adjusting the delay elements specific to each channel.

A delay chain is associated with each interface signal that allows the Deskew Controller to use the set of 16 relative delays to compensate for the skew in the TXDATA interface and to reconstruct the original alignment of the Transmit data TXDATA[15:0].

The out-of-alignment alarm (TX\_OOA) is set if a match has not been found on any of the 16 data channels. When a data match has been found on all 16 data channels, and stable skew data derived, then the Deskew algorithm is considered locked, and the TX\_OOA is cleared. Skew measurements are monitored continuously, and the TX\_OOA alarm remains cleared as long as consistent skew data is generated.

Figure 3 below shows a logical model of the Receive interface in the Kodiak Transponder. Data is striped across the 16 bit lanes of the Receive Data bus (RXDATA[15:0]) in a round-robin fashion. The first bit received is written into the re-timing buffer associated

with RXDATA[15] and the last into that associated with RXDATA[0]. The re-timing buffers act as a set of FIFOs to bridge between the optical timing domain and the Transmit interface timing domain.

RXDSC replicates the data sent on each signal of the Receive Data bus RXDATA[15:0] cyclically. The framing pattern generator is chosen first to insert the framing pattern of two A1 (F6 Hex) and two A2 (28 Hex) bytes and 4 bytes of expansion header (EH1 to EH4 are each currently set to 1010 1010 pattern when idle; their use is for further study). Then, each RXDATA[X] signal is sampled, in turn, for 64 bit times (8 bytes). Sampling begins with RXDATA[15] and ends with RXDATA[0]. After all the data lanes have been sent, a new reference frame is initiated on RXDSC and the process continuously repeats.

Table 1 below shows a reference frame on the Receive Deskew Channel (RXDSC). The 16 sets of data sample bytes are copied from the Receive Data bus RXDATA[15:0] starting with bit 15 RXDATA[15] and ending with bit 0 RXDATA[0]. In Table 1, transmission is from left to right and top to bottom.

etworks

ential

| Bit Time       | Value                      | Value                      | Value                      | Value                      | Comments                                                       |

|----------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------------------------------------------|

| 1 - 32         | A1<br>1111 0110            | A1<br>1111 0110            | A2<br>0010 1000            | A2<br>0010 1000            | Framing bytes                                                  |

| 33 - 64        | EH1<br>1010 1010           | EH2<br>1010 1010           | EH3<br>1010 1010           | EH4<br>1010 1010           | Expansion Header bytes<br>For Future Use                       |

| 65 - 96        | RXDATA[15]<br>Bits 1 - 8   | RXDATA[15]<br>Bits 9 - 16  | RXDATA[15]<br>Bits 17 - 24 | RXDATA[15]<br>Bits 25 - 32 | 64 consecutive bits from                                       |

| 97 - 128       | RXDATA[15]<br>Bits 33 - 48 | RXDATA[15]<br>Bits 41 - 48 | RXDATA[15]<br>Bits 49 - 56 | RXDATA[15]<br>Bits 57 - 64 | RXDATA[15]                                                     |

| 129 - 160      | RXDATA[14]<br>Bits 1 - 8   | RXDATA[14]<br>Bits 9 - 16  | RXDATA[14]<br>Bits 17 - 24 | RXDATA[14]<br>Bits 25 - 32 | 64 consecutive bits from                                       |

| 161 - 192      | RXDATA[14]<br>Bits 33 - 48 | RXDATA[14]<br>Bits 41 - 48 | RXDATA[14]<br>Bits 49 - 56 | RXDATA[14<br>Bits 57 - 64  | RXDATA[14]                                                     |

| 193 - 1024     |                            |                            |                            |                            | 64 consecutive bits from<br>each of RXDATA[13] to<br>RXDATA[1] |

| 1025 - 1056    | RXDATA[0]<br>Bits 1 - 8    | RXDATA[0]<br>Bits 9 - 16   | RXDATA[0]<br>Bits 17 - 24  | RXDATA[0]<br>Bits 25 - 32  | 64 consecutive bits from                                       |

| 1057 -<br>1088 | RXDATA[0]<br>Bits 33 - 48  | RXDATA[0]<br>Bits 41 - 48  | RXDATA[0]<br>Bits 49 - 56  | RXDATA[0<br>Bits 57 - 64   | RXDATA[0]                                                      |

#### Table 1 Reference Frame on RXDSC

# Timing & Clocking

Clock timing from the system side to the transponder is provided via TXREFCK and RXREFCK. The TXREFCK and RXREFCK inputs must be generated from a source that has a frequency accuracy of equal or better than the value stated in Table 12. In order for the internally generated Transmit clock frequency to have the required accuracy for operation in a SONET/SDH system, TXREFCK must strictly meet these specifications. A lower accuracy clock source may be used in applications less demanding than Additionally, in order to meet the SONET/SDH. SONET/SDH jitter specifications, the maximum Transmit reference clock jitter must be guaranteed over the 20 kHz to 320 MHz bandwidth, so that the PLL clean-up circuitry can operate properly. For details of the reference clock jitter requirements, see Table 12.

In addition to the use of TXREFCK as the clock source the transponder can also be operated using the recovered clock from the receive chain to provide the transmit clock. This configuration would be used when operating in a loop-through mode. The choice of clock source is controlled in two ways: by the hard wired pin TXCKSEL and by the I<sup>2</sup>C command register TxLINETIMESEL. For futher detail see the I<sup>2</sup>C command list in section *A.3.1.1.1 Set TX Command Register* of Appendix A. Nominally TXREFCK can be either at the data rate or at one quarter of the data rate of the SFI-5 TXDATA. The TXREFCK data rate is selected using the I<sup>2</sup>C command TxREFSEL. [Note: the rate select feature may not be available in all Transponders]. TXCKSRC is a

Transponder derived source clock that is provided for use by the system side ASICs. The framer/FEC interfacing to the module must use TXCKSRC provided by the module in order to meet the jitter and wander specifications specified in the SxI-5 implementation agreement.

# **Monitoring and Control Functions**

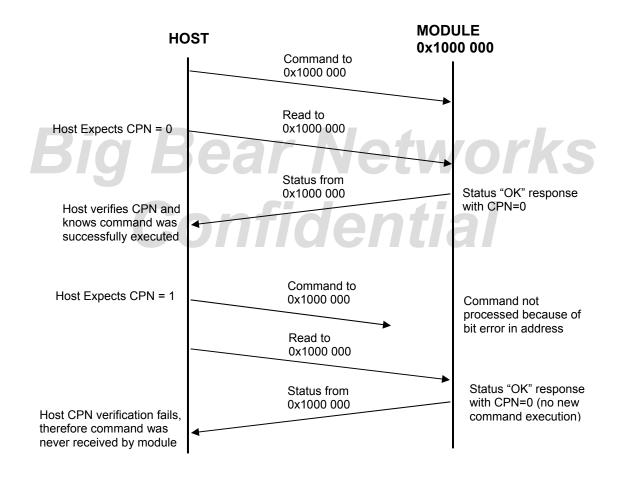

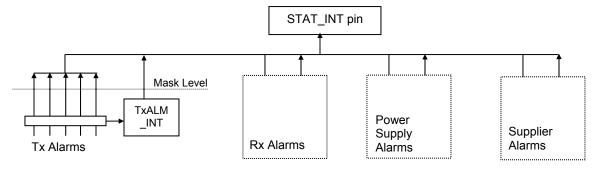

The Kodiak Transponder contains an on-board microcontroller, which provides a module management interface as well as performing additional housekeeping functions for the Transponder. The management interface is accessed via an I<sup>2</sup>C bus, which is made available via two pins on the Transponder connector. Refer to Table 14 I2C Electrical Characteristics (DC) and Table 15 I2C Electrical Characteristics (AC) for the detailed electrical specifications for the I<sup>2</sup>C interface. A three bit address I2CADDR[2:0] selects the transponder. The Kodiak Transponder operates as an I<sup>2</sup>C bus slave. In the event of an alarm condition the transponder notifies the system that an alarm has occurred via the pin ALM INT. The system can then determine the exact nature of the alarm by a request through the  $I^2C$  bus. A configurable hard-wire alarm is also available through pin CFG ALM.

The transponder occupies one fixed address in the  $I^2C$  space. The specific command protocol for the  $I^2C$  interface is provided in Appendix A.

####

# **Pin Descriptions**

Table 2 SerDes / Framer Interface – 16 x 2.488Gb/s Interface

| Name             | I/O | Туре           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXDATA[15:0]_P/N | 0   | DCML           | <b>Receive Data</b> . The Received Data signals (RXDATA) carry data from the transponder deserializer to the system ASIC. Serial optical data is striped onto RXDATA[15:0] in a round-robin fashion. RXDATA[15] contains the first bit received while RXDATA[0] the last bit received. RXDATA[15] contains the first bit of the first byte received while RXDATA[0] contains the last bit of the second byte received. RXDATA is frequency locked to RXDCK with unspecified static phase offset.                                                                                                                                                                                     |

| RXDSC_P/N        | 0   | DCML           | <b>Receive Deskew Channel.</b> The Receive Deskew Channel (RXDSC) signal provides reference data to enable skew measurements of the Receive data bus (RXDATA[15:0]). RXDSC is a 2.488 Gb/s stream. RXDSC contains reference frames consisting of 4 framing bytes, 4 bytes of expansion header, and 16 sets of 8-byte samples of each signal on the Receive data bus (RXDATA[15:0]). Samples are taken from the Receive data bus in a round-robin fashion, starting with RXDATA[15] and ending with RXDATA[0]. RXDSC is frequency locked to RXDCK with unspecified static phase offset.                                                                                               |

| Rid              |     | Re             | <b>Receive Status.</b> The Receive Status (RXS) signal carries status from the Transponder to the system ASIC. An RXS alarm indicates that RXDCK and RXDATA are not derived from the optical receive signal. RXS is an asynchronous signal which is 'active high': "0"=Normal Op., "1"=Alarm                                                                                                                                                                                                                                                                                                                                                                                         |

|                  |     |                | RXS is detected in hardware and is asynchronous with respect to the micro-<br>controller. Two conditions will cause the RXS alarm to trigger:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RXS              | 0   | LVTTL          | <ol> <li>When the CDR VCO frequency is greater than 1000ppm from the input<br/>reference clock RXREFCK. Under this condition the VCO will perform<br/>a relock search by sweeping frequency. This search may result in the<br/>RXS alarm toggling on and off until a valid lock is obtained (at which<br/>point the alarm will be off).</li> </ol>                                                                                                                                                                                                                                                                                                                                   |

|                  |     |                | <ol> <li>RXS will also trigger if the input optical power is below -10.5dBm (with<br/>1dB hysteresis). Under this condition the CDR VCO will lock to<br/>RXREFCK.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  |     |                | The response time of RXS is given below in Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RXDCK_P/N        | 0   | DCML           | <b>Receive Data Clock</b> . The Receive Data Clock (RXDCK) signal provides timing reference for the Receive data path signals (RXDATA, RXDSC). RXDCK is nominally a 50% duty cycle clock with a frequency that is one-quarter of the data bit rate of RXDATA and RXDSC. RXDCK is frequency locked to these signals. Static phase offset between RXDCK and RXDATA, RXDSC is unspecified.                                                                                                                                                                                                                                                                                              |

|                  |     |                | RXDCK tracks the frequency of the CDR VCO. Therefore if RXS triggers while the input power is below -10.5 dBm then RXDCK will lock to RXREFCK. If RXS triggers with input power above -10.5 dBm then RXDCK will sweep in frequency around RXREFCK.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RXREFCK_P/N      | I   | Diff<br>LVPECL | <b>Receive Reference clock.</b> (RXREFCK) signal is a low jitter input reference that provides timing for the Clock and Data Recovery (CDR) loop. Same frequency as TXREFCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TXDATA[15:0]_P/N | I   | DCML           | <b>Transmit Data.</b> The Transmit Data (TXDATA[15:0]) signals carry data from<br>the system-side ASIC (e.g. SONET Framer) to the transponder serializer.<br>Data on TXDATA[15:0] are placed on the transmit optical stream in a round-<br>robin fashion. TXDATA[15] contains the first bit transmitted while<br>TXDATA[0] the last bit transmitted. When TXDATA[15:0] is octet aligned,<br>TXDATA[15] contains the first bit of the first byte transmitted while<br>TXDATA[15] contains the first bit of the second byte transmitted.<br>TXDATA[0] contains the last bit of the second byte transmitted.<br>TXDATA[15:0] is frequency locked to TXDCK with unspecified static phase |

|             |   |                | offset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|---|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXDSC_P/N   | I | DCML           | <b>Transmit Deskew Channel.</b> The Transmit Deskew Channel (TXDSC) provides reference data to enable skew measurements of the Transmit data bus (TXDATA[15:0]). TXDSC is a 2.488 Gb/s or 2.689 Gb/s stream. TXDSC contains reference frames consisting of 4 framing bytes, 4 bytes of expansion header and 16 sets of 8-byte samples of each signal recovered from the Transmit data bus (TXDATA[15:0]). Samples are taken from the Transmit data bus in a round-robin fashion, starting with TXDATA[15] and ending with TXDATA[0]. TXDSC is frequency locked to TXDCK with unspecified static phase offset.                                                                                                                                                                                                                                                                                                                                                 |

| TXDCK _P/N  | I | DCML           | <b>Transmit Data Clock.</b> The Transmit Data Clock (TXDCK) signal provides timing reference for the Transmit data path signals (TXDATA, TXDSC). TXDCK is nominally a 50% duty cycle clock with a frequency that is one-quarter of the data bit rate of TXDATA and TXDSC. TXDCK is frequency locked to TXCKSRC, TXDSC, and TXDATA. Static phase offset between TXDCK and TXDATA, TXDSC is unspecified.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |   |                | This clock is not used in the Kodiak transponder, but is properly terminated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TXREFCK_P/N | 9 | Diff<br>LVPECL | <b>Transmit Reference Clock.</b> (TXREFCK) signal is a low jitter input<br>reference at either 1/64 or 1/16 of the optical transmit rate. Normally<br>TXREFCK is used as the reference for the internal clock frequency<br>synthesizer used to generate the 39.813 GHz transmit bit rate clock.<br>Internal to the transponder the frequency of TXREFCK (i.e. the 1/64 rate of<br>622 MHz, or the 1/16 rate of 2.488 GHz) is selected by the I <sup>2</sup> C command<br>TxREFSEL. The incoming signals TXDATA, and TXDSC should be<br>frequency locked to TXREFCK. Static phase offset between TXDCK,<br>TXDSC and TXDATA is unspecified.<br>Selecting between this local reference source TXREFCK or the recovered<br>line clock as the source for the transmitter reference clock is done via either<br>the I <sup>2</sup> C command, TxLINETIMESEL, as well as the hardwired pin<br>TXCKSEL. See the I <sup>2</sup> C command section for further detail. |

| TXCKSRC_P/N | 0 | DCML           | <b>Transmit Clock Source</b> . The Transmit Clock Source (TXCKSRC) signal from the transponder provides timing reference for the Transmit data path signals (TXDATA, TXDSC, TXDCK). TXCKSRC is nominally a 50% duty cycle clock with a frequency that is one-quarter of the data bit rate of TXDATA and TXDSC. TXCKSRC is derived from the master transmit bit rate clock in the CMU which is in turn derived from either the local input reference TXREFCK or recovered timing from the receive chain. (See description of TXREFCK above)                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TXMONCK     | 0 |                | <b>Transmit Monitor Clock.</b> Transmit Monitor Clock provides a single ended clock that can be used to monitor the transmit clock on the mux. For the Kodiak transponder TXMONK is at 1/16 of the transmit bit rate, i.e. 2.488 GHz. See Table 13 for electrical details. This clock signal can be turned on or off using the I <sup>2</sup> C command TxMUTEMCLK. The default state for TxMUTEMCLK has TXMONK turned off. (See the supplier reserved command section of Appendix A).                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RXMONCK     | 0 |                | <b>Receive Monitor Clock.</b> Transmit Monitor Clock provides a single ended clock that can be used to monitor the receive clock on the demux. This clock is turned off during normal operation and startup. (NOT SUPPORTED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Notes:

For OC-768 / STM-256, bit 15 is the MSB and bit 0 is the LSB. The MSB is transmitted first onto the fiber. P/N denotes the positive and negative sides of the differential signal.

####

Table 3 Dedicated Alarms and Controls

| Name      | I/O | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |     |       | <b>Transponder Reset.</b> Active on Low. "0" = reset transponder, "1" = normal operation. Resets all transponder components including CMU, CDR, and all bus registers. [10KOhm pull-up]. To trigger a reset hold the reset state for at least 100ms.                                                                                                                                                                                                                |

| MOD_RESET | I   | LVTTL | After release of reset the transponder I <sup>2</sup> C interface will be functional within 20ms and the SFI-5 interfaces will be fully functional within 500ms. The transmit optics will be enabled when their TEC controlled temperatures reach specified operating temperature of around 30C. Depending on the starting temperature this could take from 1-2 seconds for a start close to the operating point, to 30 seconds for a start temperature around 70C. |

| REG_RESET | I   | LVTTL | <b>Register Reset.</b> Active on Low. "0" = resets all bus control registers, "1" = normal operation. This resets control registers and will only affect the I2C interface. The signal path of the transponder continues to operate normally. [10K Ohm pull-up]. To trigger a reset hold the reset state for at least 100ms. The $I^2C$ interface is available 1ms after the reset is released.                                                                     |

|           |     |       | <b>Enable Laser</b> . Active on Low. "0" = laser enabled (normal operation), "1" = laser disabled. [10KOhm pull-up]                                                                                                                                                                                                                                                                                                                                                 |

| LS_ENABLE |     | LVTTL | Note that this operating state can also be changed via the I <sup>2</sup> C command LS_ENABLE which also has as its default condition a "0" for laser enabled.                                                                                                                                                                                                                                                                                                      |

|           | 9   |       | The Pin and $I^2C$ commands are 'or'd so that changing either one to 'high' will disable the laser. See the state table in the $I^2C$ section A.3.1.1.1 Set TX Command Register. The laser is fully turned on 10ms after the LS_ENABLE is turned on.                                                                                                                                                                                                                |

|           |     | Co    | <b>Loss of Signal Alarm.</b> Active on Low. "0" = Alarm, "1" = normal operation.<br>Indicates that there is no incoming optical signal. Note that this alarm<br>represents the instantaneous state of the input signal - i.e. it is not latched<br>after being triggered.                                                                                                                                                                                           |

| LOS       | 0   | LVTTL | LOS is detected in hardware and is asynchronous with respect to the micro-<br>controller. The signal is low pass filtered with a 2.5 $\mu$ sec time constant, so<br>drop-outs lasting less than 2 $\mu$ s are ignored. Loss of signal is detected<br>within 50 $\mu$ s. LOS is triggered when the input optical signal drops below -<br>10.5 dBm and will then turn off when the signal rises above -9.5dBm.                                                        |

| STAT_INT  | 0   | LVTTL | <b>Status Interrupt.</b> Active on Low. "0" = Alarm, "1" = normal operation.<br>Indicates one of the internal alarms is triggered. This signal pin has an active pull-up. The internal alarms are read over the $l^2C$ bus. Note that this alarm represents the instantaneous state of the alarms in the transponder - i.e. it is not latched after being triggered.                                                                                                |

| CFG_ALM   | ο   | LVTTL | <b>Configurable Alarm</b> . Active on Low. "0" = Alarm, "1" = normal operation.<br>An $I^2C$ configurable alarm output. Typically used for an alarm or status indicator where 'real time' indication of a change is desired. (See $I^2C$ Alarm Table for further detail on configuring this alarm). [This signal is open collector]                                                                                                                                 |

|           |     |       | <b>Transmit Clock Select.</b> Selects whether the transmit clock reference is taken from a local reference or from the recovered clock of the incoming optical data. "0" = select recovered timing, "1" = select local reference, TXREFCK. [10KOhm pull-up]                                                                                                                                                                                                         |

| TXCKSEL   | I   | LVTTL | Note that this operating state can also be changed via the I <sup>2</sup> C command TxLINETIMSEL which also has as its default condition a "1" for local timing.                                                                                                                                                                                                                                                                                                    |

|           |     |       | The Pin and $I^2C$ commands are 'or'd so that switching to recovered timing requires both pin and $I^2C$ command to be in the '0' state. See the state table in the $I^2C$ section A.3.1.1.1 Set TX Command Register                                                                                                                                                                                                                                                |

# **BIGBEAR**

#### Table 4: Alarm Response Time

| Alarm        | Respo   | onse Time (Activ | vation) | Response Time (Deactivation) |                         |       |  |

|--------------|---------|------------------|---------|------------------------------|-------------------------|-------|--|

| Alarm        | Minimum | Typical          | Maximum | Minimum                      | Minimum Typical Maximur |       |  |

| CFG_ALM      |         |                  | 10 ms   |                              |                         | 10 ms |  |

| LOS          |         |                  | 50 μs   |                              |                         | 50 μs |  |

| RXS (Note 1) | 10 μs   | 100 μs           | 10 ms   | 500 μs                       | 2 ms                    | 10 ms |  |

Note 1: Under a fault condition of constant light input with no data modulation, the RXS error signal may toggle between the 'lock-error' state and the 'no-lock-error' state.

#### Table 5 $l^2C$ Interface Bus

The transponder adheres to the 40G MSA specification for the  $I^2C$  interface. The physical interface bus is summarized in the table below with further detail given in section 2.1 of Appendix A.

| Name          | I/O | Туре              | Description                                                                 |

|---------------|-----|-------------------|-----------------------------------------------------------------------------|

| I2C_SDA       | I/O | Open<br>Collector | I <sup>2</sup> C Data line                                                  |

| I2C_SCL       | I   | Open<br>Collector | I <sup>2</sup> C Clock line                                                 |

| I2C_ADDR[2:0] |     | LVTTL             | I <sup>2</sup> C Address [2:0] Transponder 3 bit address. [1KOhm pull-down] |

The hardware layer of the interface adheres to the Philips ® Semiconductor definition of the I<sup>2</sup>C bus. The components used on the transponder are registered with Philips. The firmware interface provides a means of transferring data and control information between the host system and the transponder.

The transponder I<sup>2</sup>C address is made up of a fixed part and a configurable part. The configurable part is three bits long, and is set by the I2C\_ADDR[2:0] pins on the 300-pin MegArray connector.

| I <sup>2</sup> C Address (7 bit) | Device      |

|----------------------------------|-------------|

| 0x1000xxxR                       | Transponder |

Note: xxx = user selectable 3 bit transponder address and R = Read/Write bit.

#### **I<sup>2</sup>C Protocol Interface**

The transponder adheres to the 40G MSA specification for the  $I^2C$  interface protocol. Additional features specific to the Big Bear transponder may also be incorporated. All protocol details are provided in <u>Appendix A</u>.

#### W Ν E Т 0 R

#### Table 6: Power & Ground Signals

| Name         | I/O | Туре             | Description                                                                                                                                                                                                                                |

|--------------|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3V Digital | Ι   | Supply           | Power supply, +3.3V Digital                                                                                                                                                                                                                |

| 3.3V Analog  | Ι   | Supply           | Power supply, +3.3V Analog                                                                                                                                                                                                                 |

| APS Digital  | Ι   | Supply           | Adaptable Power Supply, Digital                                                                                                                                                                                                            |

| -5.2VDigital | I   | Supply           | Power supply, -5.2V Digital                                                                                                                                                                                                                |

| -5.2VAnalog  | Ι   | Supply           | Power supply, -5.2V Analog                                                                                                                                                                                                                 |

| 5.0VAnalog   | Ι   | Supply           | Power supply, 5.0V Analog                                                                                                                                                                                                                  |

| DigitalGND   | I   | Ground           | Digital ground                                                                                                                                                                                                                             |

| AnalogGND    | I   | Ground           | Analog ground                                                                                                                                                                                                                              |

| FM_GND       | Ι   | Ground           | Transponder Case                                                                                                                                                                                                                           |

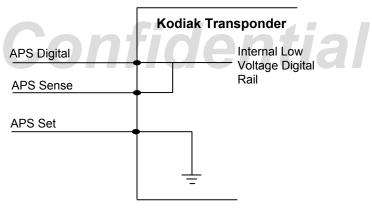

| APS Sense    | 0   | Analog<br>Signal | Zero ohm sense connection to the 1.8V internal supply of the transponder. Placeholder pin for the sense line of an adjustable power supply feature.                                                                                        |

| APS_Set      | 0   | Analog<br>Signal | Used to set the value of the APS voltage between 0.9V and 1.8V. Kodiak transponder currently operates with an APS voltage of 1.8V. The APS circuits are shown below in Figure 4. Tying APS Set to ground sets the operating state to 1.8V. |

| NuC          | NuC |                  | No user Connection. Must remain open circuits.                                                                                                                                                                                             |

| DI           | g   | De               | ar networks                                                                                                                                                                                                                                |

Figure 4 Adaptable Power Supply (APS) Lines

#### Absolute Maximum Ratings

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

#### Table 7 Absolute Maximum Ratings

| Rating                             | Symbol           | Min  | Мах                | Units |

|------------------------------------|------------------|------|--------------------|-------|

| Storage Case Temperature           | T <sub>stg</sub> | -40  | +85                | °C    |

| Receive Optical Input Power PIN    | P <sub>MAX</sub> |      | +6                 | dBm   |

| Minimum Fiber Bend Radius          |                  | 30   |                    | mm    |

| +3.3V Supplies (Note 1)            |                  | -0.3 | +3.6               | V     |

| +1.8V Supplies (Note 1)            |                  | -0.3 | +2.0               | V     |

| +5.0V Supplies                     |                  | -0.3 | +6.0               | V     |

| -5.2V Supplies                     |                  | -5.5 | +0.3               | V     |

| LV-TTL Input Voltage               |                  | -0.2 | 3.3VDigital + 0.2  | V     |

| LV-TTL Output Voltage              |                  | -0.2 | 3.3VDigital + 0.2  | V     |

| CML Output Source Current          |                  |      | 20                 | mA    |

| Static Discharge Voltage (Note 2)  | ESD              |      | 25KV Air Discharge | V     |

| Relative Humidity (non-condensing) | RH               | 15   | 85                 | %     |

Note 1: This is the maximum potential difference allowed in order to avoid device degradation during product use conditions. Note 2: Per IEC 801.2 (Class 1A product)

# **Recommended Operating Conditions**

Minimum and maximum values specified over operating case temperature range at 50% duty cycle data signal. Typical values are measured at room temperature unless otherwise noted. Note that the transponder contains internal protection circuitry which permits any power-up sequence.

#### Table 8 Standard Operating Conditions

| Parameter                            | Name             | Conditions   | Min   | Typical | Max   | Units |

|--------------------------------------|------------------|--------------|-------|---------|-------|-------|

| Operating Case Temperature           | T <sub>c</sub>   | Notes 1      | 0     |         | 70    | °C    |

| Transponder Power Consumption        | P <sub>DIS</sub> |              |       | 26      | 32    | W     |

| +3.3V Power Supply Voltage (Digital) | 3.3VDigital      |              | 3.135 | 3.3     | 3.465 | V     |

| +3.3V Power Supply Voltage (Analog)  | 3.3VAnalog       |              | 3.135 | 3.3     | 3.465 | V     |

| +1.8V Power Supply Voltage (Digital) | APS Digital      |              | 1.71  | 1.8     | 1.89  | V     |

| -5.2V Power Supply Voltage (Analog)  | -5.2VAnalog      |              | -5.45 | -5.2    | -4.95 | V     |

| -5.2V Power Supply Voltage (Digital) | -5.2VDigital     |              | -5.45 | -5.2    | -4.95 | V     |

| +5.0V Power Supply Voltage (Analog)  | +5.0VAnalog      |              | 4.75  | 5.0     | 5.25  | V     |

| +3.3V Power Supply Current (Digital) | 3.3VDigital      | Note 2       |       | 2300    | 2700  | mA    |

| +3.3V Power Supply Current (Analog)  | 3.3VAnalog       |              |       | 2500    | 3000  | mA    |

| +1.8V Power Supply Current (Digital) | APS Digital      |              |       | 700     | 1000  | mA    |

| -5.2V Power Supply Current (Analog)  | -5.2VAnalog      |              |       | 1400    | 2000  | mA    |

| -5.2V Power Supply Current (Digital) | -5.2VDigital     |              |       | 1400    | 2000  | mA    |

| +5.0V Power Supply Current (Analog)  | 5.0VAnalog       |              |       | 0       | 100   | mA    |

| Ripple and Noise                     |                  | 1Hz to 20MHz |       |         | 1%    | mVpp  |

2. The maximum transient current for the 3.3V Digital is 3500mA during TEC turn-on.

Figure 5: Recommended Temperature Measurement Points

# **Optical Characteristics**

Minimum and maximum values specified over operating case temperature range at 50% duty cycle data signal. Typical values are measured at room temperature unless otherwise noted. All values are stated for end-of-life.

| Parameter                    | Symbol                | Conditions                    | Min  | Typical | Мах  | Units |

|------------------------------|-----------------------|-------------------------------|------|---------|------|-------|

| Transmitter                  |                       |                               |      |         |      |       |

| Operating Wavelength         | λc                    |                               | 1530 | 1555    | 1565 | nm    |

| Output Power                 | Po                    |                               | 0    |         | +3   | dBm   |

| Extinction Ratio             | ER                    |                               | 8.2  |         |      | dB    |

| Spectral Width               | $\Delta\lambda_{RMS}$ | @ -20dB                       |      |         | 1    | nm    |

| Side Mode Suppression Ratio  | SMSR                  |                               | 35   |         |      | dB    |

| Receiver                     |                       |                               |      |         |      |       |

| Nominal Center Wavelength    | λ <sub>NOM</sub>      |                               | 1290 |         | 1570 | nm    |

| Stressed Sensitivity         | P <sub>IN</sub>       | @10 <sup>-12</sup> BER Note 2 | -5   |         |      | dBm   |

| Overload                     | P <sub>OL</sub>       |                               | +3   |         |      | dBm   |

| Optical Return Loss          | RL <sub>RX</sub>      |                               | 27   |         |      | dB    |

| Optical Path                 |                       |                               |      |         |      |       |

| Optical Link Loss            | OL                    |                               | 0    |         | 4    | dB    |

| Path Penalty/System Margin   | М                     | Note 2                        | 0    |         | 1    | dB    |

| Dispersion                   | D                     |                               | -40  |         | 40   | ps/nm |

| Polarization Mode Dispersion | DGD                   |                               |      |         | 7.5  | ps    |

| System Optical Return Loss   |                       |                               | 24   |         |      | dB    |

Table 9: 40G Short Reach Optical Transponder Characteristics (SR1: 5dB budget, ~2km reach, Note 1)

Notes:

1. Aligned with the ITU G.693 specification for NRZ 40G 2km applications (VSR2000-3R2, VSR2000-3R3, VSR2000-3R5)

Stressed receiver sensitivity includes worst-case ER penalty, transmitter patterning allowance, and other receiver impairments. This corresponds to a back-to-back measurement without fiber and without path penalty, per section 6.4 of ITU-T G.693.

# **Optical Transmit Eye Pattern Mask**

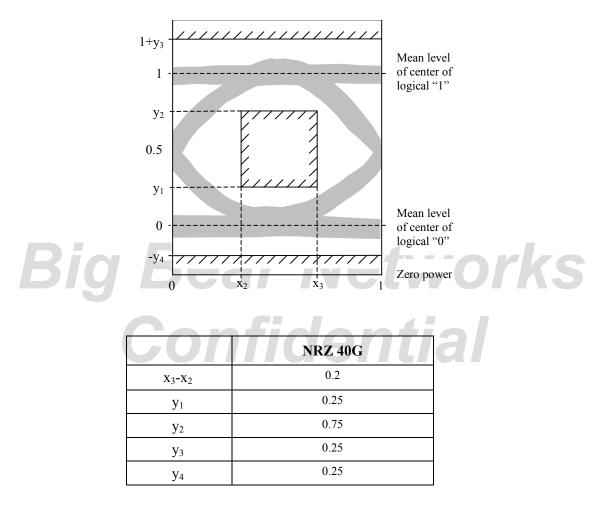

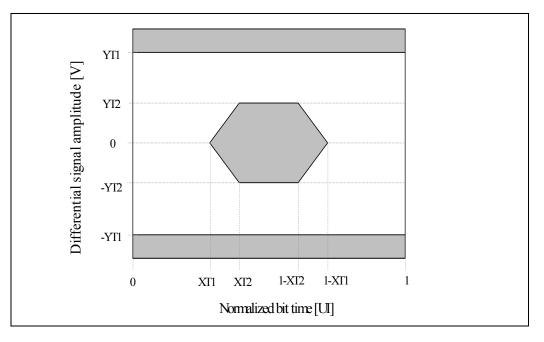

The optical eye mask satisfies the specification provided in ITU-T Recommendation G.693, "Optical interfaces for intra-office systems", October 2001. The parameters specifying the mask of the transmitter eye diagram are shown in Figure 6.

Figure 6: Mask of the eye diagram for the optical transmit signal

Note -  $x_2$  and  $x_3$  of the rectangular eye mask need not be equidistant with respect to the vertical axes at 0 UI and 1 UI.

####

# **Electrical Characteristics**

### Table 10 LV-TTL Input and Output Characteristics

| Parameter                       | Symbol          | Conditions                                   | Min | Typical | Мах | Units |

|---------------------------------|-----------------|----------------------------------------------|-----|---------|-----|-------|

| LV-TTL Input DC Characteristics |                 |                                              |     |         |     |       |

| Input High Voltage              | VIH             | TTL V <sub>CC1</sub> = Max                   | 2.0 |         | 3.6 | V     |

| Input Low Voltage               | VIL             | TTL V <sub>CC1</sub> =Min                    | 0   |         | 0.8 | V     |

| Input High Current              | I <sub>IH</sub> | V <sub>IN</sub> =2.4V                        |     |         | 50  | μA    |

| Input Low Current               | l <sub>IL</sub> | V <sub>IN</sub> =0.5V                        | -50 |         |     | μA    |

| LV-TTL Output DC Characteristic | s               |                                              |     |         |     |       |

| Output High Voltage             | V <sub>OH</sub> | V <sub>CC2</sub> =Min, I <sub>OH</sub> =-8mA | 2.4 |         |     | V     |

| Output Low Voltage              | V <sub>OL</sub> | V <sub>CC2</sub> =Min I <sub>OL</sub> = 1mA  |     |         | 0.4 | V     |

#### Table 11 CML Input and Output Characteristics

| Parameter                                                          | Symbol                 | Conditions                                                | Min  | Typical | Max  | Units |

|--------------------------------------------------------------------|------------------------|-----------------------------------------------------------|------|---------|------|-------|

| CML Differential DC-Coupled Inp<br>Applies to TXDATA[15:0], TXDCK, |                        | istics                                                    |      |         |      |       |

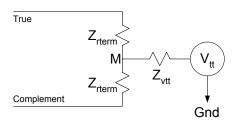

| Termination Voltage                                                | V <sub>tt</sub>        | p-p value (Note 1)                                        | 1.1  | 1.2     | 1.3  | V     |

| Input Sensitivity                                                  | VR <sub>Sense</sub>    | p-p voltage                                               | 175  |         |      | mV    |

| Bias Voltage Source Impedance                                      | ZV <sub>tt</sub>       | (Note 2)                                                  |      |         | 30   | Ω     |

| Rise/Fall Time                                                     | T <sub>Rise/Fall</sub> | 20-80%. Measured<br>differentially into a<br>100 ohm load | nti  | al      | 0.36 | UI    |

| Differential Input Voltage Swing                                   | VR <sub>IN</sub>       | VR <sub>IN</sub> p-p voltage (Note 3) 0                   |      |         | 1.15 | V     |

| Common Mode Voltage                                                | VR <sub>CM</sub>       | VR <sub>CM</sub> (Note 4)                                 |      |         | Vtt  | V     |

| Differential Input Impedance                                       | ZInDiff                | nDiff (Note 5), <i>Figure 7</i>                           |      |         | 125  | Ω     |

| Differential Return Loss                                           | L <sub>DR</sub>        | (Note 6)                                                  | 10   |         |      | dB    |

| CML Differential AC-Coupled with Applies to RXDATA[15:0], RXDCK,   |                        | Itput Characteristics                                     |      |         |      |       |

| Driver Rise/Fall Time                                              | TD <sub>RF</sub>       | 20% - 80% into 100<br>ohm load                            | 50   |         |      | ps    |

| Differential Output Voltage Swing                                  | $V_{\text{DO-CML}}$    | p-p voltage                                               | 0.6  | 0.8     | 1.0  | V     |

| Single-ended Output Impedance                                      | Z <sub>SE</sub>        | ≥ 10KHz, (Note 7)                                         | 37.5 |         | 62.5 | Ω     |

| Differential Output Impedance                                      | ZD                     | ≥ 10KHz, (Note 8)                                         | 75   |         | 125  | Ω     |

| Single-ended Return Loss                                           | R <sub>HS</sub>        | (Note 9)                                                  | 7.5  |         |      | dB    |

| Differential Return Loss                                           | RL <sub>Diff</sub>     | (Note 10)                                                 | 7.5  |         |      | dB    |

#

CML Differential DC-Coupled Output Characteristics

| Applies to TXCKSRC                |                     |                                                              |       |     |       |    |

|-----------------------------------|---------------------|--------------------------------------------------------------|-------|-----|-------|----|

| Output Common Mode Voltage        | V <sub>CM</sub>     | (Note 11)                                                    | 0.72V |     | 1.23V | V  |

| Driver Rise/Fall Time             | TD <sub>RF</sub>    | Refer to eye mask definition in <i>Table 18</i>              |       |     |       | ps |

| Differential Output Voltage Swing | V <sub>DO-CML</sub> | p-p voltage                                                  | 0.6   | 0.8 | 1.0   | V  |

| Short Circuit Current             | I <sub>Short</sub>  | To any voltage<br>between 1.45V & -<br>0.25, power on or off | -50   |     | 50    | mA |

| Single-ended Output Impedance     | Z <sub>SE</sub>     | At DC                                                        | 37.5  |     | 62.5  | Ω  |

| Differential Output Impedance     | ZD                  | At DC                                                        | 75    |     | 125   | Ω  |

| Single-ended Return Loss          | R <sub>HS</sub>     | (Note 9)                                                     | 7.5   |     |       | dB |

| Differential Return Loss          | RL <sub>Diff</sub>  | (Note 10)                                                    | 7.5   |     |       | dB |

Notes:

- 1. Specified for both AC and DC coupling applications

- 2. From DC to .75\*baud rate if DC blocking capacitors are not present. From 500Mhz to .75\*baud rate if DC blocking capacitors are present.

- 3. Peak-Peak voltage. Zrterm=62.5 ohms.

- 4. (Vhigh + Vlow) / 2

- 5. At DC. Parameter is unspecified if DC blocking capacitors are present.

- 6. From 0.004\*baud rate to 0.75\*baud rate relative to 100 ohms.

- 7. At DC the single ended output impedance is 10K ohms.

- 8. At DC the differential output impedance is 20K ohms.

- 9. From 0.004\*baud rate -0.75\*baud rate. Relative to 50 ohms.

- 10. From 0.004\*baud rate -0.75\*baud rate. Relative to 100 ohms.

- 11. (Vhigh + Vlow) / 2. When using a load of *Figure* 7 with 1.05 < Vtt < 1.35 Volts, 37.5 < rterm< 62.5 ohms, 0< Zvtt < 30 ohms. Ground in Figure 7 is the same as driver ground. Vtt values take into account the assumption of up to ± 50mV ground shift between transmit and receive. Parameter is unspecified if DC blocking capacitors are present.</p>

Figure 7 Termination and Signaling

#### Table 12: Input Reference Clock Characteristics

| Parameter                                 | Symbol                                           | Conditions                                                   | Min | Typical | Max    | Units     |

|-------------------------------------------|--------------------------------------------------|--------------------------------------------------------------|-----|---------|--------|-----------|

| Differential Input Impedance              | Z <sub>In Diff</sub>                             | AC Coupled                                                   | 90  | 100     | 110    | Ω         |

| Differential Input Voltage                | V <sub>In Diff</sub>                             | Peak - peak                                                  | 400 | 800     | 1800   | mV        |

| Nominal VCO Reference Center<br>Frequency | TXREFCK<br>RXREFCK                               |                                                              |     | 622.08  |        | MHz       |

| Nominal VCO Reference Center<br>Frequency | TXREFCK<br>RXREFCK                               | (NOT SUPPORTED see Note 1)                                   |     | 2.488   |        | GHz       |

| Reference Clock Frequency<br>Tolerance    | TXREFCK <sub>Tol</sub><br>RXREFCK <sub>Tol</sub> | ± 20ppm required to<br>meet SONET/SDH<br>output requirements | -30 |         | 30     | ppm       |

| Reference Clock Jitter                    |                                                  | 12.8 KHz to 20 KHz                                           |     |         | 2      | ps<br>rms |

| Reference Clock Input Duty Cycle          | TXREFCK <sub>DC</sub><br>RXREFCK <sub>DC</sub>   |                                                              | 45  |         | 55     | %         |

| Reference Clock Rise & Fall Times         | T <sub>R</sub> , T <sub>F</sub>                  | Note 2                                                       |     |         | 100 ps |           |

Notes:

- 1. Current versions of Kodiak transponder require TXREFCK and RXREFCK to be 1/64 of the optical transmit data rate.

- 2. An input reference clock consisting of a sine wave can also be used with a very minor increase in low frequency jitter.

## Table 13 TXMONK Specifications

| Parameter         | Conditions                              | Min        | Typical | Max    | Units |

|-------------------|-----------------------------------------|------------|---------|--------|-------|

| Output Voltage    | Single Ended Peak -<br>Peak, AC coupled | <u>Jer</u> | 400     |        | mV    |

| Nominal Frequency |                                         |            | 2.488   | 2.689  | GHz   |

| Duty Cycle        |                                         | 45         |         | 55     | %     |

| Rise & Fall Times |                                         |            |         | 100 ps |       |

# **BigBears**

#### Table 14 l<sup>2</sup>C Electrical Characteristics (DC)

| Parameter                    | Symbol           | Conditions | Min  | Typical | Max  | Units |

|------------------------------|------------------|------------|------|---------|------|-------|

| High Level Input Voltage     | VIH              |            | 1.9  |         | 5.5  | V     |

| Low Level Input Voltage      | V <sub>IL</sub>  |            | -0.5 |         | 1.65 | V     |

| Hysteresis                   | V <sub>HYS</sub> |            | 0.28 |         |      | V     |

| Low Level Output Voltage     | V <sub>OL</sub>  |            |      |         | 0.4  | V     |

| Capacitance for each I/O pin | С                |            |      |         | 10   | pF    |

#### Table 15 $l^2$ C Electrical Characteristics (AC)

| Parameter                  | Symbol              | Conditions | Min | Typical | Max | Units |

|----------------------------|---------------------|------------|-----|---------|-----|-------|

| SCL Frequency              | F <sub>SCL</sub>    |            | 0   |         | 400 | kHz   |

| Hold Time (repeated) START | t <sub>hd,sta</sub> | >100KHz    | 0.6 |         |     | μS    |

| Low Period of SCL          | t <sub>Low</sub>    | >100KHz    | 1.3 |         |     | μS    |

| High Period of SCL         | t <sub>High</sub>   | >100KHz    | 0.6 |         |     | μS    |

| Rise Time of SCL, SDA      | t <sub>Rise</sub>   |            |     |         | 300 | nS    |

| Fall Time of SCL, SDA      | t <sub>Fall</sub>   |            |     |         | 250 | nS    |

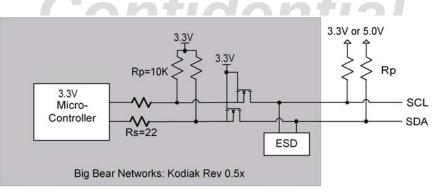

The interface operates in FAST-mode with a data transfer rate of 400Kbps, or it can operate in 100Kbps mode. The design uses level translators to ensure proper operation with any host system that uses a 3.3V or greater supply voltage. As shown in Figure 8 below, the line card needs to provide pull-up resistors for the SCL and SDA lines. The number of I<sup>2</sup>C devices in the system determines the value of the pull-up resistors Rp.

Figure 8 *l*<sup>2</sup>C Interface

#### PC Command Latency

Following a Hardware Reset

There is a 20 ms delay from the rising edge of MOD\_RESET to the time the transponder is ready to receive a command.

#### Command-to-Command

The maximum command execution latency is 125 microseconds. This specifies the time from when the last command byte has transferred to the transponder to when the transponder has executed that command and the results are available. This does not apply to Save or Restore type commands or any other command that must read or write the flash. If the system is polled before the command has finished executing it will return the response "Still Processing" (See Appendix Section A.2.6 for further detail on the status byte).

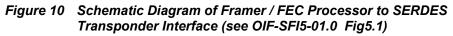

#### SFI-5 Eye Mask & Jitter Specifications

The eye mask defines the horizontal (jitter) and vertical (signal amplitude) characteristics for the SFI-5 data and clock signals. The eye masks are defined for the transponder inputs (TXDATA) and the transponder outputs (RXDATA).

The following eye mask and jitter specifications follow the OIF-SXI5-01.0 (Oct 2002) specification format. Note that the correspondence between the OIF and Kodiak Transponder parameters are shown below in *Table 16 Transport Path Parameter Correspondence*.

#### Table 16 Transport Path Parameter Correspondence

| Transport Path       | Kodiak Transponder                     | OIF-SXI5-01.0 (OCT 2002)               |

|----------------------|----------------------------------------|----------------------------------------|

| Framer/FEC to SERDES | TXDATA (SFI-5 input to Transponder)    | Receive Eye Mask: Reference Point 'D'  |

| SERDES to Framer/FEC | RXDATA (SFI-5 output from Transponder) | Transmit Eye Mask: Reference Point 'A' |

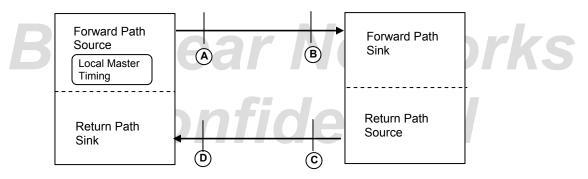

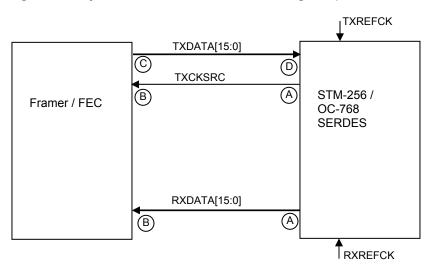

The rationale for the correspondence is shown in the following figures. Figure 9, which is taken from the OIF specification, shows the system reference points for the eye mask and jitter specifications of the OIF specification. Normally the timing for TXDATA flow is taken from the local PLL in the CMU of the Transponder. Therefore using the OIF interface definition shown in Figure 10 the TXDATA eye diagram and jitter correspond to reference point 'D'.

In the case of RXDATA the timing is also regenerated in the CDR of the transponder so the relevant reference point is 'A'.

Figure 9 Eye Mask and Jitter Reference Diagram (see OIF-SXI5-01.0 Fig 6)

#### Table 17 SFI-5 TxData Eye Mask Specifications

| Data / Clock         | XR1 (UI) | XR2 (UI) | YR1 (V) | YR2 (V) | DJ [pp Ul] | Total Jitter<br>J <sub>⊺ot</sub> [pp UI] |

|----------------------|----------|----------|---------|---------|------------|------------------------------------------|

| TXDATA (Notes 1,2,3) | 0.33     | 0.42     | 0.5     | 0.0875  | 0.35       | 0.65                                     |

| TXDCK                | 0.27     | 0.39     | 0.5     | 0.0875  | 0.24       | 0.54                                     |

Notes:

TXDATA Eye Mask Specifications taken from OIF-SXI5-01.0 (Oct 2002) Receive Eye Mask Specifications (Table 5) using reference 1. point 'D'

TXDATA received eye mask at receiver pin measured with a signal from a 100 Ohm source that has more than 20dB return loss at a 2. frequency of 1.6 \* baud rate.

The horizontal limit specified in the eye mask shown in Figure 11 represents the total jitter seen at the receiver input (both random 3. jitter and deterministic jitter).

#### Figure 12 SFI-5 RXData Eye Mask (Eye at the RXDATA output)

#### Table 18 SFI-5 RXData Eye Mask Specifications

| Data / Clock         | XT1 (UI) | XT2 (UI) | YT1 (V) | YT2 (V) | DJ [pp UI] | Total Jitter<br>J <sub>⊺ot</sub> [pp UI] |

|----------------------|----------|----------|---------|---------|------------|------------------------------------------|

| RXDATA (Notes 1,2,3) | 0.175    | 0.45     | 0.50    | 0.25    | 0.17       | 0.35                                     |

| RXDCK                | 0.15     | 0.45     | 0.50    | 0.25    | 0.12       | 0.30                                     |

| TXCKSRC              | 0.15     | 0.45     | 0.50    | 0.25    | 0.12       | 0.30                                     |

Notes:

- 1. RXDATA Eye Mask Specifications taken from OIF-SXI5-01.0 (Oct 2002) Transmit Eye Mask Specifications (Table 4) using reference point 'A'.

- 2. RXDATA eye mask at driver pin measured into a 100 Ohm load having more than 20dB return loss at a frequency of 1.6 \* baud rate.

- 3. The horizontal limit specified in the eye mask shown in *Figure 12* represents the total jitter seen at the driver output (both random jitter and deterministic jitter).

Table 19 SFI-5 Jitter Specifications

| Parameter                  | TYPE | RXDATA&<br>RXDSC<br>(Note 1) | TXDATA &<br>TXDSC<br>(Note 2) | UNITS           |

|----------------------------|------|------------------------------|-------------------------------|-----------------|

| Skew                       | Data | 2.0                          | 5.0                           | UI peak         |

| Correlated Wander          | All  | 4.5                          | 10.0                          | UI peak to peak |

| Uncorrelated Wander        | All  | 0.60                         | 0.65                          | UI peak to peak |

| Total Wander               | All  | 5.1                          | 10.65                         | UI peak to peak |

| Relative Wander            | All  | 1.2                          | 1.3                           | UI peak to peak |

| Skew + (Relative Wander)/2 | Data | 2.6                          | 5.65                          | UI peak         |

Notes:

1. RXDATA Jitter Specifications taken from OIF-SXI5-01.0 (Oct 2002) (Table 3) using reference point 'A'.

2. TXDATA Jitter Specifications taken from OIF-SXI5-01.0 (Oct 2002) (Table 3) using reference point 'D'

# **Jitter Characteristic**

It is the intention that the Kodiak Transponder be compatible with future (in-development) OC-768 / STM-256 ANSI and ITU jitter specifications. The specifications given herein are derived from G.693 and the ongoing work within the ITU on the specification of G.8251 (formerly G.otnjit) for OTU3 interfaces with ODU3 Clock (ODC) ODCb requirements.

#### **Jitter Generation**

Jitter generation is specified to comply with G.8251 and G.693 requirements. The first of these essentially limits the amount of random jitter generated by the transponder. The jitter generation shall not exceed the values given in *Table 20 G.8251 OTU3 Jitter Generation Limits* for a 60-second measurement interval using a jitter filter with the indicated bandwidths. Specifically, the jitter band-pass filter possesses 0dB mid-band gain, a 20dB/decade roll-off below F0 and a 60-dB/decade roll-off above F1.

| Measurement | F0 (kHz) | F1 (MHz) | <b>Ј (UI-р-р)</b> <sup>1</sup> |

|-------------|----------|----------|--------------------------------|

| Wide-Band   | 20       | 320      | 1.2                            |

| High-Band   | 16,000   | 320      | 0.1                            |

Table 20 G.8251 OTU3 Jitter Generation Limits

Note 1. The unit of 1 UI is defined to be 23.25ps for 43 Gb/s operation, and should be scaled for 39.8131 Gb/s use. See G.8251, Rev. 4.0, Table A.2.

The second set of requirements limits the total high-frequency (i.e. untracked) jitter, including deterministic and random sources. These requirements are still in the process of being defined. The Kodiak Transponder will be compatible with applicable industry standards, G.693.

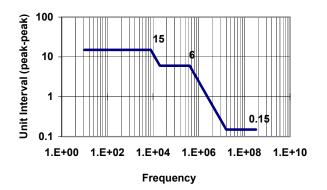

#### Jitter Tolerance

The jitter tolerance meets or exceeds the requirements for OTU3 interfaces, the details of which are provided below. Values taken from G.8251 Table 4.

| Table 21 | G.8251 | OTU3 | Interface | Jitter | Tolerance |

|----------|--------|------|-----------|--------|-----------|

|----------|--------|------|-----------|--------|-----------|

| F1 (kHz) | F2 (kHz) | F3 (kHz) | F4 (kHz) | F5 (MHz) |

|----------|----------|----------|----------|----------|

| 8        | 20       | 400      | 16,000   | 320      |

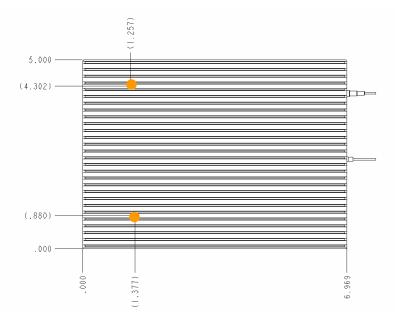

Figure 13 G.8251 OTU3 Interface Jitter Tolerance Mask (UI peak-peak)

Kodiak SR 40G Rev 0.99e 7/9/03

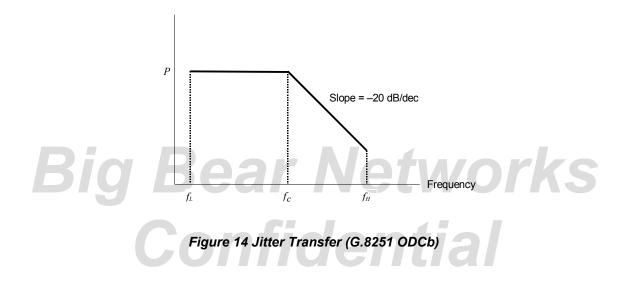

### Jitter Transfer

The Jitter transfer will be less than 0.1 dB peaking up to 16 KHz corresponding to ODCb type systems. *Table 22 Jitter Transfer* below shows the ODU3 ODCb break frequencies.

| Table 22 Jitter Transfer | Table 2 | 2 Jitter | <sup>r</sup> Transfer |

|--------------------------|---------|----------|-----------------------|